EECS 31L/CSE 31L: Lab 1

Digital Design Lecture Videos for Lab 1

- Logic Gates (pdf): English | Mandarin | Spanish

- Logic Components (pdf): English | Mandarin | Spanish

- Hierarchical Components (pdf): English | Mandarin | Spanish

- Digital Design Idol: Boolean Algebra

Digital Design Example Videos for Lab 1

Sample Lab Handout

Lab 1 Handout

-

"; print ""; // special linking for lab 1 since main page is publicly accessible. remember to update the link for not logged in as well. if ($auth_object->isLoggedIn()) { if ($auth_object->allowedAccess($auth_object->EECS31L_ARRAY)) { print "View Lab 1 Handout"; } else if ($auth_object->allowedAccess($auth_object->EECS31L_STUDENT_ARRAY)) { print "View Lab 1 Handout"; } else { print "View Lab 1 Handout"; } print ""; } else { // you're not logged in, sorry... print "View Lab 1 Handout"; } ?>

Digital Design Refresher for Lab 1

Available on EECS 31/CSE 31 Course Page

- Boolean Algebra

- Boolean Simplification

- Logic Gates

- Technology Mapping

Lab 1 Quiz Sample Problems

Sample Problem 1

Question

The following VHDL code for gate level logic does not compile and simulate correctly with ModelSim as written below. In the table below, rewrite the minimum number of lines to make the entire code compile and simulate correctly.

Solution

Line # Code 10 end final_prob1; 13 process (k, p, s) Detailed Explanation

View Video Explanation for Problem 1

Sample Problem 2

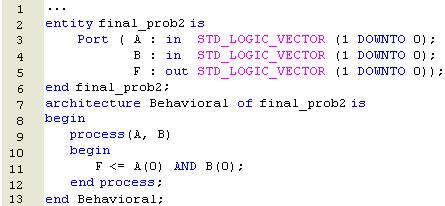

Question

The following VHDL code for an AND function of two 2-bit vectors A and B does not compile and simulate correctly with ModelSim. In the table below, rewrite the minimum number of lines so that code correctly simulates.

Solution

Line # Code 11 F <= A AND B; or: 11 F <= (A(1) AND B(1)) & (A(0) AND B(0)); Detailed Explanation

View Video Explanation for Problem 2

Sample Problem 3

Question

Fix the given code for testing a DUT for 60 ns so it generates the test vectors from the time diagram in Figure 1.

Figure 1: Test Vector

Solution

Line # Code 16 WAIT FOR 10 ns; 18 WAIT FOR 20 ns; 24 WAIT; Detailed Explanation

View Video Explanation for Problem 3

Sample Problem 4

Question

Complete the port map of the given VHDL code so it correctly implements the following design:

Solution

Line # Code 18 And2_1: And2 PORT MAP (i0, i2, n1); 19 And2_2: And2 PORT MAP (n2, i1, d); 20 CustHW: CustomHW PORT MAP (n1, n2); Detailed Explanation