**Digital Design**

## **Logic Gates**

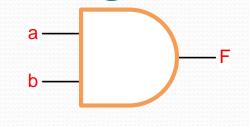

ARCHITECTURE And2\_beh OF And2 IS BEGIN

PROCESS(a,b)

BEGIN

F <= a AND b AFTER 2.4 NS;

END PROCESS;</pre>

END And2\_beh;

```

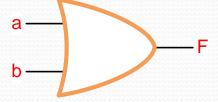

ARCHITECTURE Or2_beh OF Or2 IS

BEGIN

```

```

PROCESS(a,b)

BEGIN

F <= a OR b AFTER 2.4 NS;

END PROCESS;</pre>

```

END Or2\_beh;

a—\_\_\_\_\_F

ENTITY Inv IS PORT (a: IN std\_logic; F: OUT std\_logic);

END Inv;

ARCHITECTURE Inv\_beh OF Inv IS BEGIN

```

PROCESS(a)

BEGIN

F <= NOT a AFTER 1 NS;

END PROCESS;</pre>

```

END Inv\_beh;

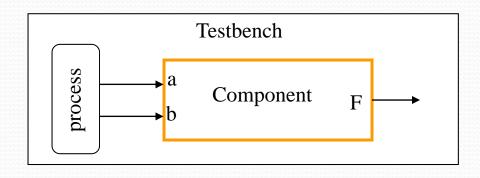

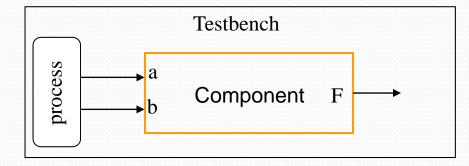

## Simulation and Testbenches

LIBRARY ieee; USE ieee.std\_logic\_1164.ALL;

ENTITY Testbench IS END Testbench;

ARCHITECTURE TBarch OF Testbench IS COMPONENT And2 IS PORT (a: IN std\_logic; b: IN std\_logic; F: OUT std\_logic); END COMPONENT;

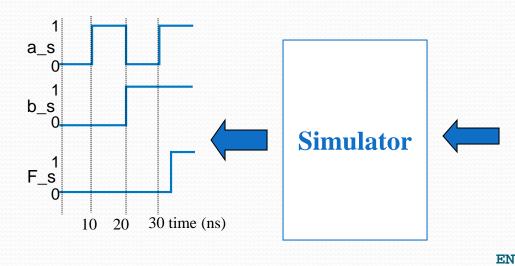

SIGNAL a\_s, b\_s, F\_s: std\_logic;

```

BEGIN

CompToTest: And2 PORT MAP (a_s, b_s, F_s);

```

```

PROCESS

BEGIN

-- Test all possible input combinations

b_s <= '0'; a_s <= '0';

WAIT FOR 10 ns;

b_s <= '0'; a_s <= '1';

WAIT FOR 10 ns;

b_s <= '1'; a_s <= '0';

WAIT FOR 10 ns;

b_s <= '1'; a_s <= '1';

WAIT;

END PROCESS;

END TBarch;</pre>

```