# An Efficient Procedure for the Synthesis of Fast Self-Testable Controller Structures

Sybille Hellebrand, Hans-Joachim Wunderlich

Institute of Computer Structures

University of Siegen

Germany

### **Abstract**

The BIST implementation of a conventionally synthesized controller in most cases requires the integration of an additional register only for test purposes. This leads to some serious drawbacks concerning the fault coverage, the system speed and the area overhead. A synthesis technique is presented which uses the additional test register also to implement the system function by supporting self-testable pipeline-like controller structures. It will be shown, that if the need of two different registers in the final structure is already taken into account during synthesis, then the overall number of flipflops can be reduced, and the fault coverage and system speed can be enhanced. The presented algorithm constructs realizations of a given finite state machine specification which can be trivially implemented by a self-testable structure. The efficiency of the procedure is ensured by a very precise characterization of the space of suitable realizations, which avoids the computational overhead of previously published algorithms.

#### 1 Introduction

The increasing demand for highly reliable micro-electronic systems in various safety-critical applications prompts for extremely high quality standards, which have to be guaranteed by refined testing techniques. Built-in self-test (BIST) is of particular importance, because it allows an efficient production testing and the capabilities for pattern generation and test response evaluation on chip can also be used for periodic maintenance tests [1].

Often the BIST is implemented by so-called multi-functional test registers like the well-known BILBO which are able to work as a system register, to generate test patterns and to compress the test responses by signature analysis. Such registers have been developed for random, deterministic, pseudo-exhaustive, and weighted random pattern test-

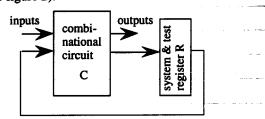

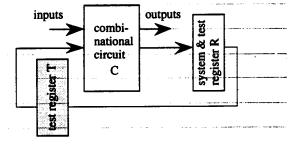

ing [4, 9, 17, 20, 26]. However, in general it is not possible to use one multi-functional register for test pattern generation and test response evaluation concurrently, since this way the required properties of the test patterns can only be ensured in some special cases [12, 14, 19]. In most cases two different registers are necessary to generate the patterns and to compress the test responses. Conventional synthesis procedures for controllers and even most of the advanced synthesis techniques for sequentially irredundant and easily testable controllers do not take into account this fact [2, 5, 6, 7, 10, 11, 13, 22, 23, 24]. They usually provide a circuit structure as shown in figure 1, which has to be complemented by an extra test register for BIST (see figure 2).

Figure 1: Conventionally synthesized controller structure.

Figure 2: Required modifications for BIST.

During test mode the register T is used as pattern generator and the multi-functional register R is configured as signature analyzer, during system mode T must be transparent. This configuration with an extra register only for test purposes has some serious drawbacks:

1) The number of flipflops must be doubled.

This work was supported by EP 7107 ARCHIMEDES.

Permission to copy without fee all or part of this material is granted, provided that the copies are not made or distributed for direct commercial advantage, the ACM copyright notice and the title of the publication and its date appear, and notice is given that copying is by permission of the Association for Computing Machinery. To copy otherwise, or to republish, requires a fee and/or specific permission.

- In system mode the test register T must be transparent or bypassed. This prolongs the critical path and may slow down the system speed of the controller.

- 3) There are faults on the feedback lines from R to the inputs of C which are not detected, as these lines are not completely exercised during self-test. This holds, even if the connections between R and T are tested in an additional step.

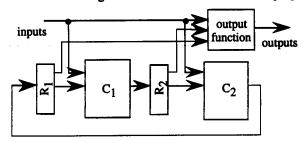

The above mentioned drawbacks can be avoided if the required additional test register T is also used to implement the system function. This results in a pipeline-like structure as shown in figure 3 and described in detail in [18].

Figure 3: Controller target structure.

A state of the controller is represented by the contents of both registers R<sub>1</sub> and R<sub>2</sub>, and the state transition function is implemented by two independent combinational circuits C<sub>1</sub> and C<sub>2</sub>. Clearly none of the registers needs to be transparent during system mode and there is no additional delay imposed this way. The self-test can be performed in two sessions by alternatively using one of the registers for pattern generation and the other for signature analysis. Moreover, as there is no transparency mode or bypassing a complete fault coverage is possible. In general the registers R and T of figure 1b are wider than the registers R<sub>1</sub> and R<sub>2</sub> of the proposed target structure, hence the structure of figure 3 needs less flipflops then the selftestable structure of figure 1b. Furthermore, also the combinational circuits C<sub>1</sub> and C<sub>2</sub> are smaller than the original circuit. As a consequence the critical path in C1, C2 and the output function is shorter than in the circuit C of figure 1. This allows higher clock rates and thus leads to a higher system performance.

It is important to note that this structure is different from structures provided by decomposition techniques where the resulting submachines contain internal feedback loops [16, 3, 15]. In [18] a computationally expensive search procedure was used for a feasibility study of the approach. In this paper a computationally efficient synthesis procedure for target structures as shown in figure 3 is presented, which makes the approach generally applicable. In contrast to known approaches trying to reduce dependencies between state variables by appropriate state coding the presented procedure relies on algebraic structure theory to address the problem already at the finite state machine

level [25, 8]. The theoretical basis of the work is a very precise characterization of the search space.

The organization of the paper is as follows: In section 2 the main results of [18] are briefly summarized. Subsequently in section 3 the main theorem for a precise characterization of the search space is proven and an efficient search procedure is developed. Section 4 provides experimental results achieved for a collection of finite state machine benchmarks [McEl 93]. Conclusions are given in section 5.

# 2 Partition Pairs and Self-Testable Realizations

The problem of synthesizing controller structures compatible with BIST can be reduced to the problem of constructing suitable realizations of the original finite state machine specifications.

Throughout this work it is assumed that a controller is fully specified as a mealy-type finite state machine  $M = (S, I, O, \delta, \lambda)$  with a finite non-empty set of states S, a finite non-empty set of inputs I, a finite non-empty set of outputs O, a next state function  $\delta : S \times I \to S$  and an output function  $\lambda : S \times I \to O$ .

To guarantee that a finite state machine can be implemented by a self-testable structure it is necessary to require some additional properties.

**Definition 1:** Let  $M = (S, I, O, \delta, \lambda)$  be a finite state machine. M is called a *finite state machine supporting a self-testable structure*, if and only if there are sets  $S_1$  and  $S_2$  and functions  $\delta_1 \colon S_1 \times I \to S_2$ ,  $\delta_2 \colon S_2 \times I \to S_1$ , such that  $S = S_1 \times S_2$  and  $\delta((s_1, s_2), i) = (\delta_2(s_2, i), \delta_1(s_1, i))$  holds for all  $s = (s_1, s_2) \in S$  and  $i \in I$ .

Obviously the straightforward implementation of such a finite state machine with logic blocks for  $\delta_1$ ,  $\delta_2$  and  $\lambda$  and registers for  $S_1$  and  $S_2$  provides a self-testable structure as shown in figure 3.

Self-testable controllers can therefore be synthesized from finite state machine specifications in two steps. First a finite state machine which realizes the specification and which supports a self-testable structure is constructed and then state coding and logic minimization algorithms are applied to this realization. A precise definition of the term realization can be found in [16, 18].

In [18] it has been shown that self-testable realizations for a finite state machine  $M = (S, I, O, \delta, \lambda)$  correspond to specific pairs of equivalence relations on the set of states S. In the following equivalence relations on S will always be considered as subsets  $L \subset S \times S$ . This way the set theoretic operators " $\cap$ " (intersection) and " $\cup$ " (union) are defined for equivalence relations and there is a partial ordering on the set of equivalence relations given by " $\subset$ " (sub-

set). The intersection of two equivalence relations is again an equivalence relation, but the union need not be transitive. Therefore an operator "+" is defined for equivalence relations by  $v_1 + v_2 := (v_1 \cup v_2)^t$ , where  $v_1^t$  denotes the transitive closure of a relation  $v_1^t$ . For an equivalence relation  $v_1^t$  and  $v_2^t$  and an element  $v_1^t$  of equivalence class is denoted by  $v_1^t$ . The set  $v_1^t$  of equivalence classes completely specifies  $v_1^t$ , and for convenience we describe  $v_1^t$  mostly by  $v_1^t$  and not by enumerating all the pairs.

**Definition 2:** Let  $M = (S, I, O, \delta, \lambda)$  be a finite state machine, and let  $(0, \delta) \subset S \times S$  be equivalence relations on S.  $(0, \delta)$  is called a partition pair for M, if and only if  $((s, t) \in (0, \delta) )$  is a partition pair, too, then  $(0, \delta)$  is called a symmetric partition pair.

For the construction of self-testable realizations symmetric partition pairs are of special interest. The following theorem has been shown in [18]:

Theorem 1: Let  $M = (S, I, O, \delta, \lambda)$  be a finite state machine. Let  $\bullet$  denote the equivalence of states and let  $(*, \bullet)$  be a symmetric partition pair for M satisfying  $* \cap \bullet \subseteq A$ . Let  $M^* = (S^*, I^*, O^*, \delta^*, \lambda^*)$  be defined by

- (i)  $S^* := S/4 \times S/4$ ,  $I^* := I$ ,  $O^* := O$ ,

- (ii)  $\delta^*((s_1, s_2), i)) := (\delta_2(s_2, i), \delta_1(s_1, i))$  with  $\delta_1(([s]_{\bullet_i}, i)) := [\delta(s, i)]_{\bullet_i}$  and  $\delta_2([s]_{\bullet_i}, i)) := [\delta(s, i)]_{\bullet_i}$ , and

(iii)

$$\lambda^*((s_1, s_2), i) :=$$

$$\begin{cases} \lambda(s, i) & \text{if } s_1 \cap s_2 \neq \emptyset \text{ and } s \in s_1 \cap s_2 \\ o^* & \text{else} \end{cases}$$

where  $o^* \in O$  is an arbitrary output value. Then  $M^*$  is a finite state machine supporting a self-testable structure which realizes M.

Theorem 1 is illustrated by the following example.

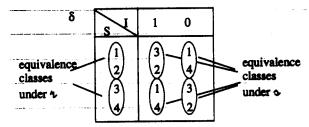

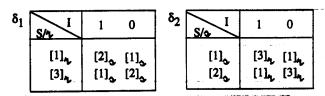

Example 1: Figure 4 shows the next state table of a small finite state machine. By  $S/\hbar = \{\{1, 2\}, \{3, 4\}\}$  and  $S/\delta = \{\{1, 4\}, \{2, 3\}\}$  a symmetric partition pair  $(\hbar, \delta)$  with  $\hbar \cap \delta \subset \bullet$  is defined.

Figure 4: Effect of a partition pair (4, 4) on the next state table of a finite state machine.

The resulting mappings  $\delta_1$ : S/ $\iota \times I \to S/\mathfrak{a}$  and  $\delta_2$ : S/ $\mathfrak{a} \times I \to S/\iota$ , which provide the state transition function  $\delta^*$ , are shown in figure 5.

Figure 5: Tables for  $\delta_1: S/4 \times I \rightarrow S/4$  and  $\delta_2: S/4 \times I \rightarrow S/4$ .

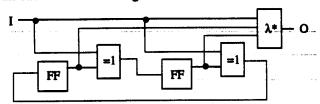

If  $[1]_{h}$  and  $[1]_{h}$  are both encoded by 1 and  $[3]_{h}$  and  $[2]_{h}$  are encoded by 0, then the constructed finite state machine  $M^* = (S/h \times S/h, I, O, h^*, h^*)$  can be implemented by the structure shown in figure 6.

Figure 6: Structure of M\*.

Theorem 1 has two consequences for the synthesis of self-testable controllers. Firstly, there is always a trivial self-testable realization for a given finite state machine  $M = (S, I, O, \delta, \lambda)$ , since the identity relation  $A \subset S \times S$  provides a symmetric partition pair  $A \subset S$ . The resulting finite state machine  $A = (S/A \times S/A \times I, O, \delta^*, \lambda^*)$  corresponds to simply "doubling" the original machine. Secondly, the problem of finding an optimal self-testable realization with small registers of about equal size can be formulated as follows:

**Problem OSTR** (Optimal Self-Testable Realization): Let  $M = (S, I, O, \delta, \lambda)$  be a finite state machine. Find a symmetric partition pair (4, 5) with  $4 \cap 5 \subset 6$ , such that

- (i)  $\lceil \log_2 |S/\nu| \rceil + \lceil \log_2 |S/\nu| \rceil$  is minimal, and

- (ii)  $\left| \frac{|S/\tau|}{|S/\tau|} 1 \right|$  is minimal

for all pairs satisfying (i).

In the next section an algorithm for OSTR will be developed, which is based on an efficient enumeration procedure for symmetric partition pairs.

# 3 An Efficient Algorithm for OSTR

In the previous section it has been shown that the problem of synthesizing self-testable controllers can be reduced to finding suitable symmetric partition pairs. The algorithm to be developed in this paragraph rigorously exploits the symmetry requirement in order to restrict the search to a small number of candidate pairs. It is based on the notion of "mm-pairs" which will be introduced in the sequel. **Definition 3:** Let  $M = (S, I, O, \delta, \lambda)$  be a finite state machine and let  $\Upsilon$ ,  $S \subset S \times S$  be equivalence relations. Then  $m(\Upsilon)$  denotes the  $\subset$ -minimal equivalence relation, such that  $(\Upsilon, m(\Upsilon))$  is a partition pair, and M(S) denotes the  $\subset$ -maximal equivalence relation, such that (M(S), S) is a partition pair.  $(\Upsilon, S)$  is called an Mm-pair, if both  $M(S) = \Upsilon$  and  $m(\Upsilon) = S$  hold. If  $m(S) = \Upsilon$  and  $m(\Upsilon) = S$  are both true, then  $(\Upsilon, S)$  is called an Mm-pair.

The Mm-pairs for a finite state machine can be regarded as the skeleton for the set of all partition pairs [16], and the basic procedure for OSTR described in [18] used an enumeration procedure for the set of Mm-pairs. Since Mm-pairs need not be symmetric, this resulted in an unnecessary computational overhead. In the following it will be shown that the set of symmetric partition pairs can be directly characterized by mm-pairs. By definition of the moperator an mm-pair is a symmetric partition pair. To show that it is sufficient to concentrate on mm-pairs some more theoretical effort is required. The first result derived from the symmetry property concerns the iterative construction of an mm-pair from an initial relation p. With  $m^{i}(p)$  denoting the relation  $m(m^{i-1}(p))$ , where  $m^{0}(p) := p$ , the following lemma can be shown.

Lemma 1: Let  $M = (S, I, O, \delta, \lambda)$  be a finite state machine, and let  $\wp \subset S \times S$  be an equivalence relation. Then the relations

$$m^{\text{even}}(\boldsymbol{p}) := \sum_{i=0}^{\infty} m^{2i}(\boldsymbol{p}) \text{ and } m^{\text{odd}}(\boldsymbol{p}) := \sum_{i=0}^{\infty} m^{2i+1}(\boldsymbol{p})$$

constitute an mm-pair  $(m^{\text{even}}(p), m^{\text{odd}}(p))$ . Furthermore, if  $(\uparrow, \diamond)$  is any symmetric partition pair with  $p \subset \uparrow$ , then  $m^{\text{even}}(p) \subset \uparrow$  and  $m^{\text{odd}}(p) \subset \diamond$ .

Some useful properties of the operators meven and modd can inductively be derived from the corresponding properties of the m-operator proven in [16].

Observation 1: Let  $M = (S, I, O, \delta, \lambda)$  be a finite state machine, and let  $v, o \subset S \times S$  be equivalence relations. Then  $m^{even}(v + o) = m^{even}(v) + m^{even}(o)$  and  $m^{odd}(v + o) = m^{odd}(v) + m^{odd}(o)$ .

Observation 2: Let  $M = (S, I, O, \delta, \lambda)$  be a finite state machine, and let  $\gamma \subset S \subset S \times S$  be equivalence relations. Then  $m^{even}(\gamma) \subset m^{even}(\gamma)$  and  $m^{odd}(\gamma) \subset m^{odd}(\gamma)$ .

The following characterization of symmetric partition pairs is an immediate consequence of lemma 1.

Theorem 2: Let  $M = (S, I, O, \delta, \lambda)$  be a finite state machine, and let  $^{*}$ ,  $^{*}$   $^{*}$   $^{*}$  S × S be equivalence relations. The pair  $(^{*}$ ,  $^{*}$ ) is a symmetric partition pair, if and only if there is an mm-pair  $(^{*}$ \*,  $^{*}$ \*) with  $^{*}$ \*\*  $^{*}$ \* and  $^{*}$ \*  $^{*}$   $^{*}$   $^{*}$   $^{*}$   $^{*}$   $^{*}$

With respect to problem OSTR it is important to note, that an mm-pair (\*\*, \*\*) has the minimal intersection of

all pairs in  $\{(\iota, \diamond) \mid \iota = \iota^*$  and  $\diamond^* \subset \diamond \subset M(\iota^*)\}$ , i.e. if  $\iota^* \cap \diamond^* \not\subset \bullet$ , then  $\iota \cap \diamond \not\subset \bullet$  for all pairs in  $\{(\iota, \diamond) \mid \iota = \iota^*$  and  $\diamond^* \subset \diamond \subset M(\iota^*)\}$ . Consequently, if the set of mm-pairs does not provide a better solution than  $(\iota \cdot \iota \cdot \iota \cdot \iota \cdot \iota)$  for OSTR, then there is no better solution at all. Furthermore, using theorem 2 it is possible to derive all solutions from the solutions found in the set of mm-pairs. Therefore the search space can be restricted to mm-pairs, and the algorithm for OSTR will be based on an efficient procedure to enumerate the set of mm-pairs.

It is possible to construct the set of mm-pairs from the base relations  $\mathfrak{B}(S) := \{ p_{s,t} \mid s,t \in S \}$ , where  $p_{s,t} := id$   $\cup \{(s,t),(t,s)\}$  is the equivalence relation identifying the states s and t in S and distinguishing all other states.

By lemma 1 an mm-pair  $(^{\bullet}, ^{\bullet})$  is characterized by  $m^{\text{even}}(^{\bullet}) = ^{\bullet}$  and  $m^{\text{odd}}(^{\bullet}) = ^{\bullet}$ . Thus the set of all mm-pairs for a finite state machine  $M = (S, I, O, \delta, \lambda)$  is described by  $\mathcal{R}_{mm}(M) := \{ (m^{\text{even}}(^{\bullet}), m^{\text{odd}}(^{\bullet})) | ^{\bullet} \subset S \times S \}$

is an equivalence relation }. Obviously,  $\tau = \sum_{(s,t) \in \tau} p_{s,t}$  is

true for any equivalence relation, and  $\mathcal{R}_{mm}(M) = \{ (m^{\text{even}}(r), m^{\text{odd}}(r)) | r = \sum_{p \in \mathcal{P}} p, \mathcal{P} \subset \mathfrak{B}(S) \}.$

Therefore  $\mathcal{R}_{mm}(M)$  can be constructed by enumerating all possible sums of relations in  $\mathfrak{B}(S)$  and calculating the corresponding mm-pair with the help of the  $m^{\text{even}_-}$  and the  $m^{\text{odd}_-}$  operator. However, this would require a computational effort of  $O(2^{|S|^2})$ . In fact, only those relations in  $\mathfrak{B}(S)$  have to considered which lead to different mm-pairs. To make this more precise a partial ordering " $\leq$ " on equivalence relations is introduced as follows:

**Definition 4:** Let  $M = (S, I, O, \delta, \lambda)$  be a finite state machine, and let  $\mathcal{L}, \mathcal{L} \subset S \times S$  be equivalence relations. Then  $\mathcal{L}$  is said to *dominate*  $\mathcal{L}$  ( $\mathcal{L} \leq \mathcal{L}$ ), if and only if  $m^{even}(\mathcal{L}) \subset m^{even}(\mathcal{L})$ .  $\mathcal{L}$  and  $\mathcal{L}$  are called *mm-equivalent* ( $\mathcal{L} \sim \mathcal{L}$ ), if both  $\mathcal{L} \leq \mathcal{L}$  and  $\mathcal{L} \leq \mathcal{L}$  are true.

It is easily verified that ~ is in fact in equivalence relation, and observations 1 and 2 provide the following observation:

**Observation** 3: Let  $M = (S, I, O, \delta, \lambda)$  be a finite state machine, and let  $\mathcal{L}, \mathcal{L} \subset S \times S$  be equivalence relations. Then  $\mathcal{L} \leq \mathcal{L}$  implies  $m^{\text{even}}(\mathcal{L}) = m^{\text{even}}(\mathcal{L} + \mathcal{L})$ .

For mm-equivalent relations  $^{*}\sim ^{*}$  observation 3 yields  $m^{even}(^{*})=m^{even}(^{*}+^{*})=m^{even}(^{*})$  and therefore the same mm-pair is obtained from  $^{*}$  and  $^{*}$ . To construct the set of all mm-pairs it is sufficient to consider the quotient space  $3(S)/\sim$ .

**Theorem 3:** Let  $M = (S, I, O, \delta, \lambda)$  be a finite state machine, and let  $\sim$  denote the mm-equivalence of relations.

Then the set of mm-pairs for M is characterized by  $\mathcal{R}_{mm}(M) =$

$$\{(\mathbf{m}^{\text{even}}(\mathbf{r}),\,\mathbf{m}^{\text{odd}}(\mathbf{r}))\,|\,\mathbf{r}=\sum_{\boldsymbol{p}\in\mathcal{P}}\mathbf{p}\;,\,\mathcal{P}\subset\mathfrak{A}(\mathbf{S})/\!\!\sim\}.$$

Making use of theorem 3 and observation 1 the following basic search tree (V, E) can be constructed to enumerate all mm-pairs. First the quotient  $\mathfrak{B}(S)/\sim$  is computed. This computation also provides the set  $\mathfrak{m}^{\text{even}} := \{\mathfrak{m}^{\text{even}}(v) \mid v \in \mathfrak{B}(S)/\sim \}$ . With  $\mathfrak{m}^{\text{even}} = \{\mathfrak{m}_1, \mathfrak{m}_2, \dots \}$  ordered arbitrarily (V, E) is defined by:

$$V := \mathcal{P}(m^{even})$$

E :=

$$\{ (\mathcal{N}_1, \mathcal{N}_2) \in V \times V \mid \mathcal{N}_2 = \mathcal{N}_1 \cup \{m_k\} \text{ with } k > \max\{i \mid m_i \in \mathcal{N}_1\} \}$$

The root of the search tree is  $\emptyset$ . Each vertex in this tree corresponds to a subset  $\mathscr{N} \subset \mathfrak{m}^{\text{even}}$  and provides an mm-pair  $(n, \mathfrak{m}(n))$  with  $n := \sum_{i=1}^n \mathfrak{m}_i$ . The tree has

mm-pair

$$(n, m(n))$$

with  $n := \sum_{m_i \in \mathcal{N}} m_i$ . The tree has  $O(2^{|m^{even}|})$  vertices and in general  $|m^{even}|$  is much

$O(2^{|m|})$  vertices and in general |m| is much smaller than  $|S|^2$ , which already leads to an enormous reduction of the computational effort compared to the straightforward approach. In addition to that, observation 3 shows that edges  $(\mathcal{N}, \mathcal{N} \cup \{m\})$  in the search tree with

$$m \le n := \sum_{m_i \in \mathcal{N}} m_i$$

can be omitted, since in this case

$m^{even}(n + m) = m^{even}(n)$ . Therefore a reduced tree  $(V^*, E^*)$  with

$$E^* := \left\{ (\mathcal{N}_1, \mathcal{N}_2) \in V \times V \mid \mathcal{N}_2 = \mathcal{N}_1 \cup \{m_k\} \text{ with } k > \max\{i \mid m_i \in \mathcal{N}_1\} \text{ and } m_k \leq \sum_{m_i \in \mathcal{N}_1} \right\}$$

is sufficient to get all mm-pairs.

To solve problem OSTR the tree  $(V^*, E^*)$  can be traversed using a breadthfirst or depthfirst strategy. For each vertex  $\mathcal N$  the relation  $n := \sum_{m_i \in \mathcal N} m_i$  is calculated. If

$m(n) \cap n \subset 0$  is true, then the mm-pair (n, m(n)) is a solution for OSTR. The costs

$$\lceil \log_2 |S/m(n)| \rceil + \lceil \log_2 |S/n| \rceil$$

and  $\left| \frac{|S/m(n)|}{|S/n|} - 1 \right|$

are calculated for this pair and compared to the lowest costs obtained so far. Finally the solution with minimal costs is selected to realize the specification.

The specific requirements of problem OSTR provide another criterion to prune the search tree and make the basic procedure computationally more efficient.

**Lemma 2:** Let  $M = (S, I, O, \delta, \lambda)$  be a finite state machine, and let  $(V^*, E^*)$  be the search tree defined above.

For

$$(\mathcal{N}_1, \mathcal{N}_2) \in E$$

let  $n_1 := \sum_{m_i \in \mathcal{N}_1} m_i$  and  $n_2 :=$

$$\sum_{\mathbf{m}_i \in \mathscr{N}_2} \mathbf{m}_i. \text{ If } \mathbf{m}(\mathbf{n}_1) \cap \mathbf{n}_1 \not\subset \bullet, \text{ then } \mathbf{m}(\mathbf{n}_2) \cap \mathbf{n}_2 \not\subset \bullet.$$

As a consequence of lemma 2, once a node  $\mathcal N$  in the searchtree with  $m(n) \cap n \not\subset \bullet$  is reached, all of its successors have this property and the subtree rooted at  $\mathcal N$  can be discarded.

# 4 Experimental results

The algorithm for problem OSTR described in section 3 has been implemented as a depthfirst procedure and has been applied to the finite state machine benchmarks distributed for the International Workshop on Logic Synthesis '93 [21]. For incompletely specified finite state machines don't care transition were fixed to transitions with next state = present state and output don't cares were set to zero. For 23 examples a nontrivial solution of OSTR (i.e. a solution different from (id, id)) could be found. Table 1 shows the results in more detail for some of these examples.

| Name      | ISI | I S <sub>1</sub> I | IS <sub>2</sub> I | # FFs<br>(conven-<br>tional) | # FFs<br>(OSTR) |

|-----------|-----|--------------------|-------------------|------------------------------|-----------------|

| bbara     | 10  | 7                  | 7                 | 8                            | 6               |

| bbsse*    | 16  | 8                  | 8                 | 8                            | 6               |

| beecount* | 7   | 4                  | 6                 | 6                            | 5               |

| dk16      | 27  | 21                 | 23                | 10                           | 10              |

| dk512     | 15  | 11                 | 14                | 8                            | 8               |

| ex1*      | 20  | 17                 | 19                | 10                           | 10              |

| mark1*    | 15  | 11                 | 6                 | 8                            | 7               |

| planet*   | 48  | 44                 | 45                | 12                           | 12              |

| s1488     | 48  | 44                 | 45                | 12                           | 12              |

| s1494     | 48  | 44                 | 45                | 12                           | 12              |

| s208      | 18  | 10                 | 10                | 8                            | 8               |

| shiftreg  | 8   | 2                  | 4                 | 6                            | 3               |

| sse*      | 16  | -8                 | 8                 | 8                            | 6               |

| tav       | 4   | 2                  | 2                 | 4                            | 2               |

| tbk       | 32  | 16                 | 16                | 10                           | 8               |

Table 1: Results of depthfirst search procedure for problem OSTR (incompletely specified examples are marked with an asterisk).

Column 2 contains the number of states of the specification. Columns 3 and 4 show the number of states in the factors  $S_1$  and  $S_2$  of the best realization found, and

columns 5 and 6 list the required number of flipflops for a conventional BIST and for an optimized BIST structure based on the presented approach. The results show that for eight examples the number of flipflops required for the optimized structure is less than for a conventional BIST. For shiftreg and tay even the lower bound  $|S_1| \cdot |S_2| = |S|$  is achieved and the number of flipflops is reduced to 50%. In terms of hardware costs the gain is even higher, because the transparent register for the conventional solution is more costly to implement than the registers used for the presented approach.

Since the overall hardware costs for both alternatives can only be compared after state coding and logic minimization, a state coding algorithm is currently being developed which takes advantage of the self-testable decomposition. A prototype version of this algorithm followed by ESPRESSO was used to determine the required PLA area for the circuits  $C_1$ ,  $C_2$  and the output function  $\lambda$  [5]. The PLA area for the circuit C of a conventional implementation was determined by applying NOVA to the finite state machine specifications [24]. In both cases the PLA area was estimated by  $(2 \cdot i + o) \cdot p$ , with i, o, p denoting the number of inputs, the number of outputs and the number of product terms, respectively. Table 2 shows the results.

| Name             | area<br>for C <sub>1</sub> | area<br>for C <sub>2</sub> | area<br>for λ | total<br>area Σ | area<br>for C | <u>Σ</u> |

|------------------|----------------------------|----------------------------|---------------|-----------------|---------------|----------|

| bbara            | 320                        | 320                        | 108           | 748             | 550           | 1.36     |

| bbsse*           | 351                        | 252                        | 546           | 1149            | 990           | 1.16     |

| beecount*        | 126                        | 90                         | 8             | 224             | 228           | 0.98     |

| dk16             | 1045                       | 931                        | 432           | 2408            | 1584          | 1.52     |

| dk512            | 224                        | 182                        | 114           | 520             | 323           | 1.61     |

| ex1*             | 1053                       | 1161                       | 1815          | 4029            | 2652          | 1.52     |

| planet*          | 2272                       | 2304                       | 3420          | 7996            | 4539          | 1.76     |

| s1488            | 2738                       | 2701                       | 3355          | 8794            | 7473          | 1.18     |

| s1494            | 2808                       | 2736                       | 3528          | 9072            | 7897          | 1.15     |

| <del>s2</del> 08 | -17 <del>6</del> -         | 176-                       | 210           | 562             | 780           | 0.72     |

| shiftreg         | 3                          | 12                         | 3             | 18              | 96            | 0.19     |

| sse*             | 351                        | 252                        | 546           | 1149            | 990           | 1.16     |

| tav              | 3                          | 3                          | 128           | 134             | 198           | 0.68     |

Table 2: Comparison of PLA areas for conventional implementations and optimized self-testable realizations.

The results show that for all examples the PLA area for the circuits  $C_1$ ,  $C_2$  and the output function is smaller than the PLA area for C. Therefore it can be assumed that in a multi-level implementation the critical path in each combinational logic block of the self-testable implementation is shorter than in the logic block of a conventional implementation. Higher clock rates and a higher performance can thus be expected. For four examples even the total PLA area for the circuits  $C_1$ ,  $C_2$  and the output function together is less than the PLA area for the conventional implementation. Moreover, for all examples the total PLA area is smaller than the area obtained by simply doubling the original network C. This is true even for planet, s1488 and s1494 were the specification with 48 states could only be decomposed into factors with 44 and 45 states, respectively.

Table 3 compares the computational effort for the presented algorithm and the basic algorithm used in [18]. For both procedures the size IVI of the search tree and the number of the nodes that have to be investigated to find the optimal solution are listed.

| Name      | ISI | log <sub>2</sub> IVI | # nodes<br>investi-<br>gated | log <sub>2</sub> iVi<br>[18] | # nodes<br>investi-<br>gated<br>[18] |

|-----------|-----|----------------------|------------------------------|------------------------------|--------------------------------------|

| bbara     | 10  | 7                    | 19                           | 43                           | 815                                  |

| bbsse*    | 16  | 43                   | timeout                      | •                            |                                      |

| beecount* | 7   | 15                   | .85                          | •                            | •                                    |

| dk16      | 27  | 20                   | 15437                        | 206                          | 337041                               |

| dk512     | 15  | 15                   | 221                          | 56                           | 343853                               |

| ex1*      | 20  | 10                   | 53                           | •                            |                                      |

| mark1*    | 15  | 45                   | timeout                      | -                            |                                      |

| planet*   | 48  | 9                    | 75                           | -                            | -                                    |

| s1488     | 48  | 9                    | 75                           | •                            | •                                    |

| \$1494    | 48  | 9                    | 75                           | • , **                       |                                      |

| s208      | 18  | 28                   | 255                          | •                            |                                      |

| shiftreg  | 8   | 17                   | 811                          | 7                            | 49                                   |

| sse*      | 16  | 43                   | timeout                      | •                            | •                                    |

| tav       | 4   | 5                    | 21                           | 7                            | 47                                   |

| tbk       | 32  | 11                   | - 55                         |                              |                                      |

Table 3: Computational effort for exhaustive search.

The results confirm that the presented approach is able to characterize the search space significantly better than the procedure used in [18]. For example for dk16 the search tree can be reduced from  $2^{206}$  to  $2^{20}$  nodes. Moreover, the impact of lemma 2 on the computational effort can be seen clearly. For almost all examples the optimal solution could be found by investigating only a small number of nodes. The limit of 500 000 nodes (timeout) was reached only by bbssee, mark1 and sse. But as table 1 indicates, for these examples a large number of possible solutions could be found before the limit was reached. All examples which did not provide a non-trivial solution could be identified quickly.

# 5 Conclusions

Pipeline-like controller structures implement the states of the specification by two different multi-functional system registers. A self-test can be performed in two sessions without any extra hardware by alternatingly using the registers for test pattern generation and signature analysis. This architecture increases the fault coverage as well as the system performance.

An efficient algorithm has been presented to generate minimal pipelined realizations from state transition diagrams. The proposed algorithm relies on algebraic structure theory to construct realizations which can be trivially implemented by a self-testable structure. The efficiency of the procedure is ensured by a very precise characterization of the space of suitable realizations, the theoretical basis of which is the newly introduced concept of mm-pairs.

The experimental results show that in general a shorter critical path and thus a higher performance can be expected. In many cases the number of flipflops is less than the respective number for a conventional BIST, and in some cases even the total PLA area is reduced. This confirms that not only higher speed and fault coverage can be obtained this way, but also area can be saved.

## References

- 1 V. D. Agrawal, C. R. Kime, K. K. Saluja: A Tutorial on Built-In Self-Test, Part 1: Principles, IEEE Design & Test of Computers, Vol. 10, No. 1, March 1993, pp. 73-82

- P. Ashar, S. Devadas: Irredundant Interacting Sequential Machines Via Optimal Logic Synthesis, IEEE Trans. on CAD, Vol. 10, No. 3, March 1991, pp. 311-325

- P. Ashar, S. Devadas, A. R. Newton: A Unified Approach to the Decomposition and Re-decomposition of Sequential Machines, Proc. 27th ACM/IEEE Int. Design Automation Conf., 1990, pp. 601-606

- 4 Z. Barzilai, D. Coppersmith, A. L. Rosenberg: Exhaustive Generation of Bit Patterns with Applications to VLSI Self-Testing, IEEE Trans. on Computers, Vol. c-32, No. 2, February 1983, pp. 190 - 194

- 5 R. K. Brayton, G. D. Hachtel, C. T. McMullen: Logic Minimization Algorithms for VLSI Synthesis, Kluwer Academic Publishers, Boston, The Hague, Dordrecht, Lancaster, 1984

- 6 R. K. Brayton et al.: MIS: A Multiple-Level Logic Optimization System, IEEE Trans. on CAD, Vol. CAD-6, No. 6, 1987, pp. 1062-1081

- 7 V. D. Agrawal, K.-T. Cheng: Finite State Machine Synthesis with Embedded Test Function, Journal of Electronic Testing Theory and Applications, Vol. 1, No. 3, October 1990, pp. 221-228

- 8 K.-T. Cheng, V. D. Agrawal: State Assignment for Testable Design, Int. Journal of Computer Aided VLSI Design, Vol. 3., March 1991

- 9 W. Daehn, J. Mucha: Hardware Test Pattern Generation for Built-In Test, Proc. IEEE Int. Test Conf., Philadelphia, 1981, pp. 100 - 113

- 10 S. Devadas, K. Keutzer: A Unified Approach to the Synthesis of Fully Testable Sequential Machines, IEEE Trans. on CAD, Vol. 10, No. 1, January 1991, pp. 39-50

- 11 S. Devadas et al.: MUSTANG: State Assignment of Finite State Machines Targeting Mulitlevel Logic Implementations, IEEE Trans. on CAD, Vol. 7, No. 12, Dec. 1988, pp. 1290-1300

- 12 B. Eschermann, H.-J. Wunderlich: Parallel Self-Test and the Synthesis of Control Units, Proc. 2nd European Test Conf., Munich, 1991

- 13 B. Eschermann, H.-J. Wunderlich: Optimized Synthesis Techniques for Testable Sequential Circuits, IEEE Trans. on CAD, Vol. 11, No. 3, March 1992, pp. 301-312

- 14 R. Gage: Structured CBIST in ASICS; Proc. IEEE Int. Test Conf., Baltimore, Maryland, 1993, pp. 332-338

- 15 Martin Geiger, Thomas Müller-Wipperfürth: FSM Decomposition Revisited: Algebraic Structure Theory Applied to MCNC Benchmark FSMs, Proc. 28th ACM/IEEE Design Automation Conf., San Francisco, 1991, pp. 182-185

- 16 J. Hartmanis, R. E. Stearns: Algebraic Structure Theory of Sequential Machines, Prentice Hall, Englewood Cliffs, 1966

- 17 S. Hellebrand, H.-J. Wunderlich, O. Haberl: Generating Pseudo-Exhaustive Vectors for External Testing; Proc. IEEE Int. Test Conf., Washingtion, D. C., 1990, pp. 670-679

- 18 S. Hellebrand, H.-J. Wunderlich: Synthesis of Self-Testable Controllers, in: Proc. EDAC/ETC/EuroAsic '94, Paris, Feb. 1994, pp. 580-585

- 19 K. Kim, D. Ha, J. Tront: On Using Signature Registers as Pseudorandom Pattern Generators in Built-in Self Testing, IEEE Trans. on CAD, Vol. 7, 1988, pp. 919-928

- 20 B. Koenemann, J. Mucha, G. Zwiehoff: Built-in Logic Block Observation Techniques, Proc. IEEE Int. Test Conf., Cherry Hill, N. J., 1979, pp. 37 - 41

- 21 K. McElvain: IWLS'93 Benchmark Set: Version 4.0, distributed as part of the IWLS'93 benchmark distribution

- 22 I. Pomeranz, S. M. Reddy: Design and Synthesis for Testability of Synchronous Sequential Circuits Based on Strong-Connectivity, Proc. IEEE 23rd Int. Symp. on Fault-Tolerant Computing, FTCS-23, Toulouse, June 1993, pp. 492-501

- 23 G. Saucier, M. C. De Paulet, P. Sicard: ASYL: A Rule-Based System for Controller Synthesis, IEEE Trans. on CAD, Vol. CAD-6, No. 6, Nov. 1987, pp. 1088-1097

- 24 T. Villa, A. Sangiovanni-Vincentelli: NOVA: State Assignment of Finite State Machines for Optimal Two-Level Logic Implementations, Proc. 26th ACM/IEEE Design Automation Conf., Las Vegas, 1989, pp. 327-332

- 25 P. Weiner, E. J. Smith: Optimization of Reduced Dependencies for Synchronous Sequential Machines, IEEE Trans. on Electronic Computers, Vol. EC-16, No. 6, Dec. 1967, pp. 835-847

- 26 H.-J. Wunderlich: Self Test Using Unequiprobable Random Patterns, Proc. IEEE 17th Int. Symp. on Fault-Tolerant Computing, FTCS-17, Pittsburgh, 1987, pp. 258-263