## Principles Of Digital Design

#### C to RTL

# Control/Data flow graphs Finite-state-machine with data IP design

- Component selection

- Connection selection

- Operator and variable mapping

- Scheduling and pipelining

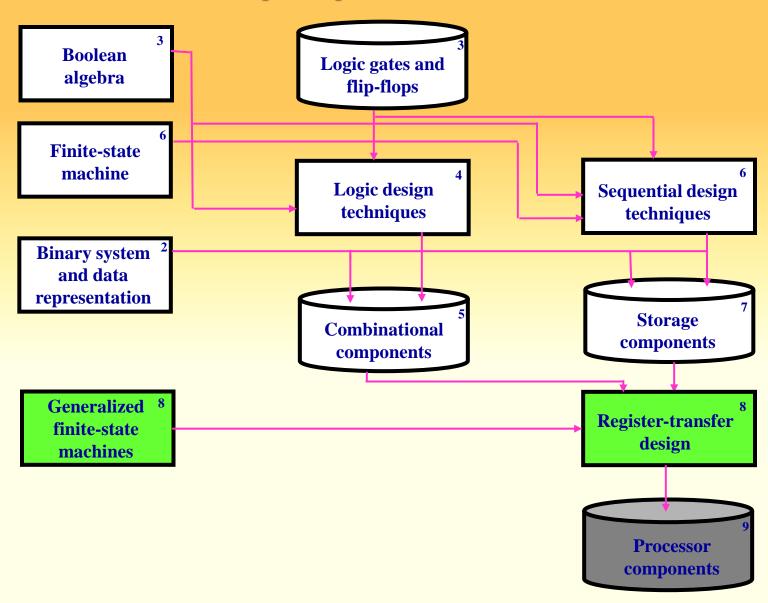

#### **Topic preview**

#### Register-transfer-level design

- Each standard or custom IP components consists of one or more datapaths and control units.

- To synthesize such IP we use the models of a CDFG and FSMD.

- We demonstrate IP synthesis (RTL Design) including

- component and connectivity selection,

- expression mapping

- scheduling and pipelining

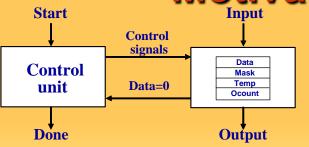

#### **Motivation: Ones-counter**

#### **Problem:**

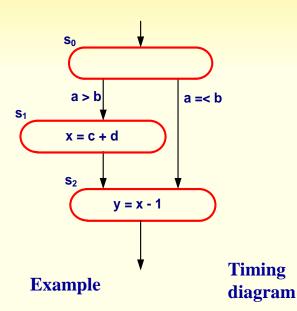

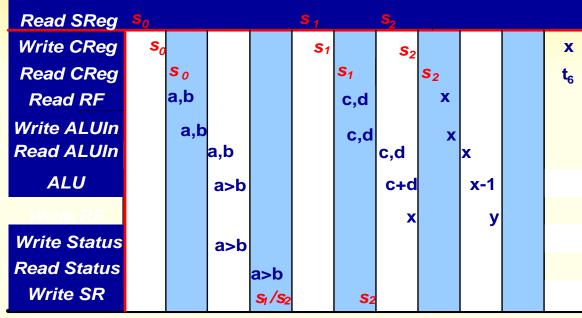

Generate controller & control words for given FSMD & Datapath

#### 20-bit control words

#### **Ones Counter from C Code**

#### Programming language semantics

- Sequential execution,

- Coding style to minimize coding

#### •HW design

- Parallel execution,

- Communication through signals

```

int OnesCounter(int Data){

01:

02:

int Ocount = 0;

03:

int Temp, Mask = 1;

04:

while (Data > 0) {

05:

Temp = Data & Mask;

06

Ocount = Data + Temp;

07:

Data >>= 1;

08:

09:

return Ocount;

10:

```

```

01:

while(1) {

while (Start == 0);

02:

03:

Done = 0;

04:

Data = Input;

Ocount = 0;

05:

06:

Mask = 1;

07:

while (Data>0) {

08:

Temp = Data & Mask;

09:

Ocount = Ocount + Temp;

10:

Data >>= 1;

11:

}

12:

Output = Ocount;

13:

Done = 1;

14:

```

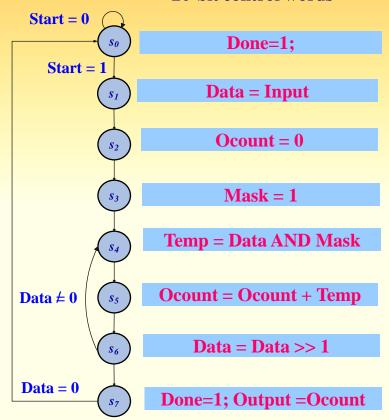

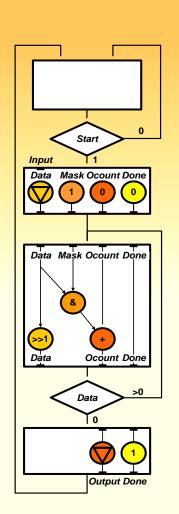

#### **CDFG for Ones Counter**

```

01:

while(1) {

02:

while (Start == 0);

03:

Done = 0;

04:

Data = Input;

05:

Occupt = 0;

06:

Mask = 1;

07:

while (Data>0) {

08:

Temp = Data & Mask;

09:

Ocount = Ocount + Temp;

10:

Data >>= 1i

11:

12:

Output = Ocount;

13:

Done = 1;

14:

```

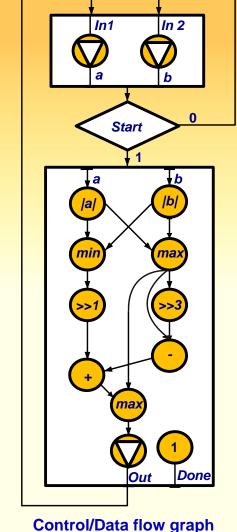

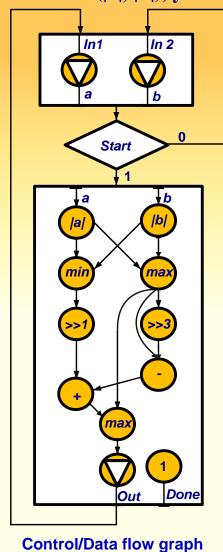

#### **Control/Data flow graph**

- •Resembles programming language

- Loops, ifs, basic blocks(BBs)

- •Explicit dependencies

- •Control dependences between BBs

- •Data dependences inside BBs

- •Missing dependencies between BBs

**RTL-based** C code

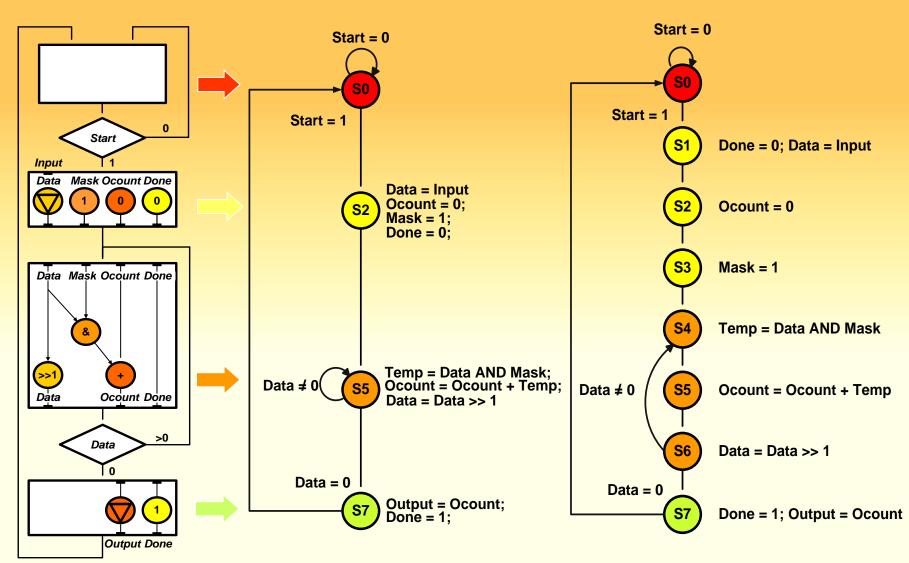

### **CDFG to FSMD for Ones Counter**

**Cycle-accurate FSMD**

**Super-state FSMD**

**CDFG**

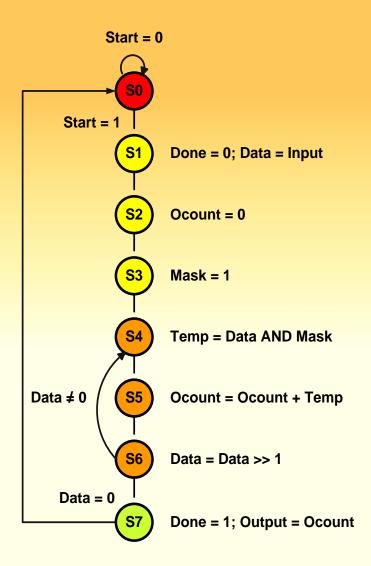

#### **FSMD** for Ones Counter

#### •FSMD more detailed then CDFG

- States may represent clock cycles

- Conditionals and statements executed concurrently

- All statement in each state executed concurrently

- •Control signal and variable assignments executed concurrently

- •FSMD includes scheduling

- •FSMD doesn't specify binding or connectivity

#### **FSMD Definition**

We defined an FSM as a quintuple < S, I, O, f, h > where S is a set of states, I and O are the sets of input and output symbols:

$$f: S \times I \longrightarrow S$$

, and  $h: S \longrightarrow O$

More precisely,

$$I = A1 \times A2 \times ... Ak$$

$S = Q1 \times Q2 \times ... Qm$

$O = Y1 \times Y2 \times ... Yn$

Where Ai, is an input signal, Qi, is the state register output and Yi, is an output signal.

To define a FSMD, we define a set of variables,  $V = V_1 \times V_2 \times ... V_q$ , which defines the state of the datapath by defining the values of all variables in each state with the set of expressions Expr(V):

Expr(V) = Const  $\bigcup V \bigcup \{e_i \# e_j | e_i, e_j \text{ el of Expr}(V), \# \text{ is an operation}\}$

- Notes: 1. Status signal is a signal in I;

- 2. Control signals are signals in O;

- 3. Datapath inputs and outputs are variables in V

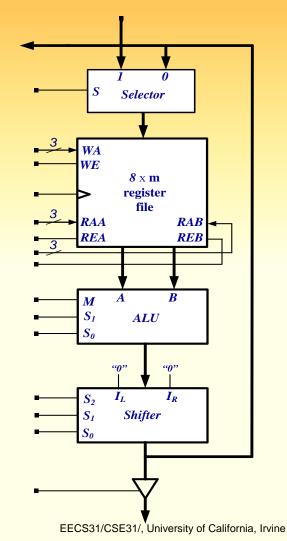

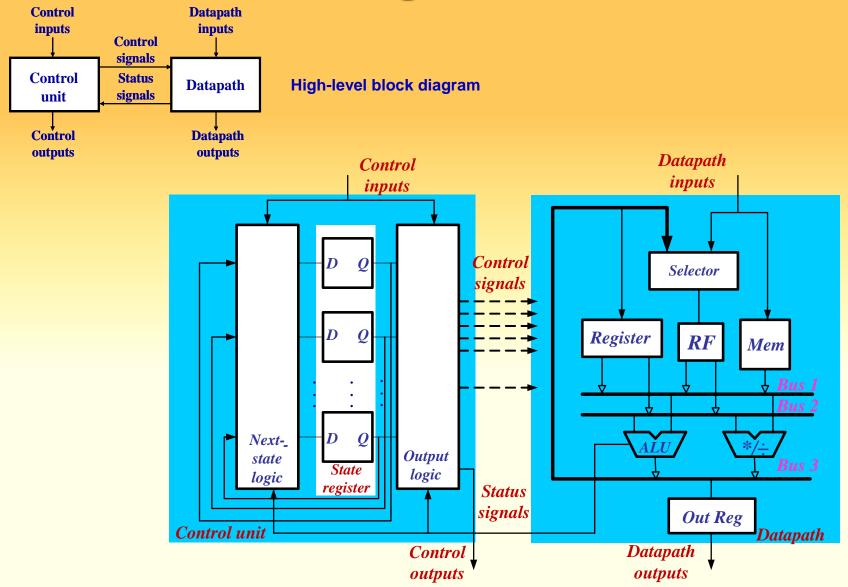

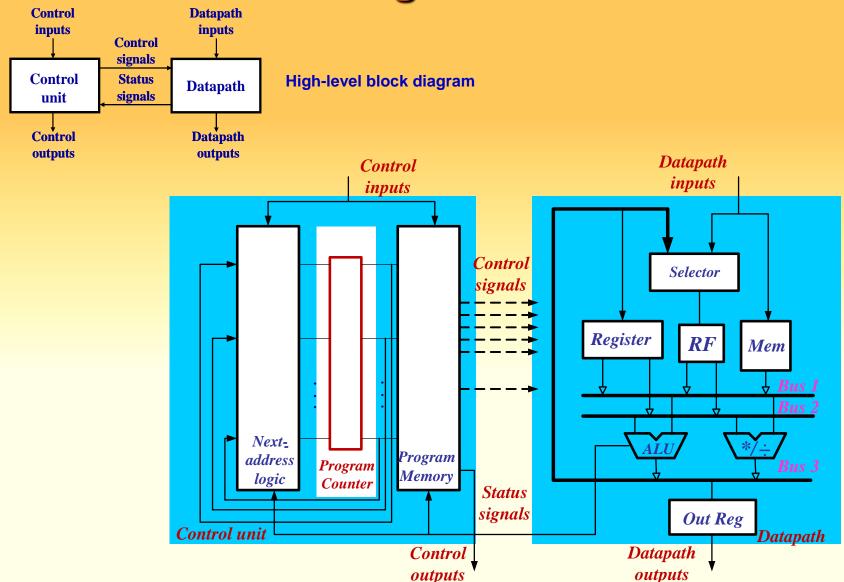

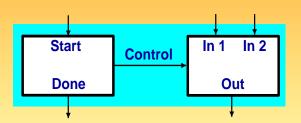

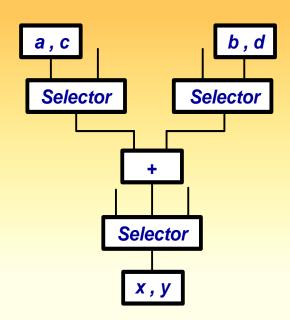

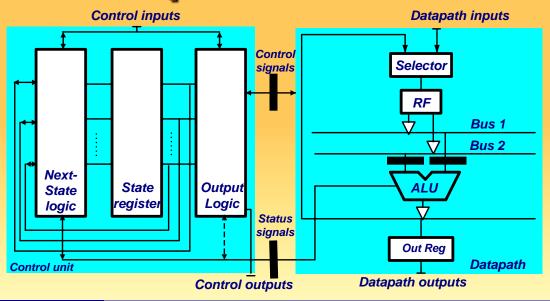

### RTL Design Model

Register-transfer-level block diagram

### RTL Design Model

Register-transfer-level block diagram

#### C-to-RTL design

- RTL generation requires definition of

- controller

- datapath

- RTL generation of a controller requires choice of

- state register (program counter)

- output logic (program memory)

- next-state logic (next-address generator)

- RTL generation of a datapath

- RTL component and connectivity selection,

- expression mapping (variable and operation mapping)

- scheduling and pipelining

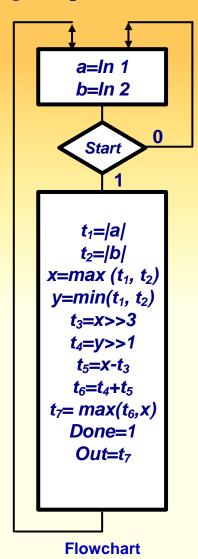

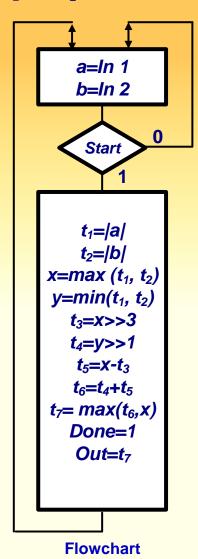

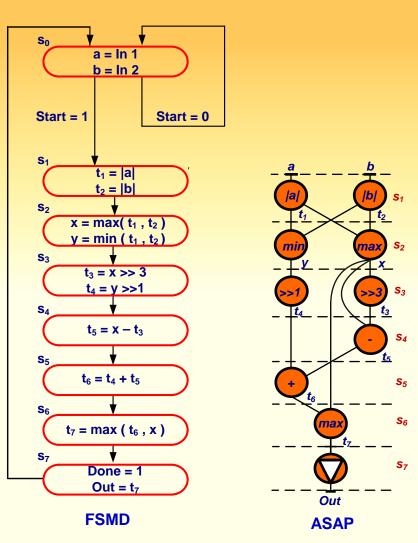

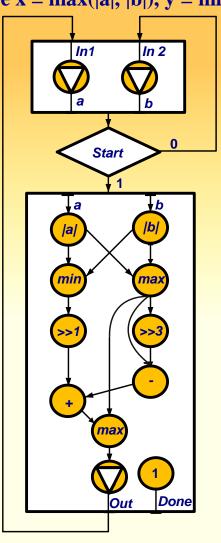

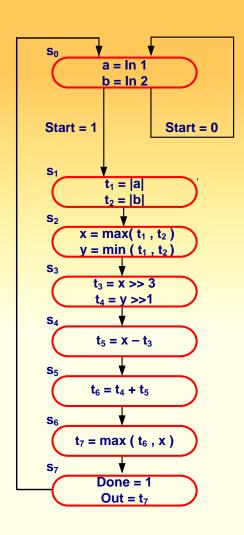

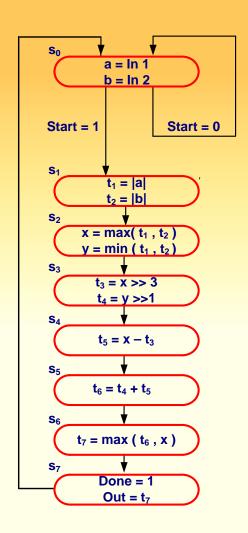

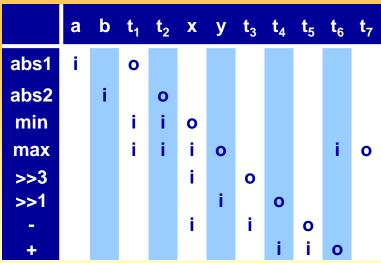

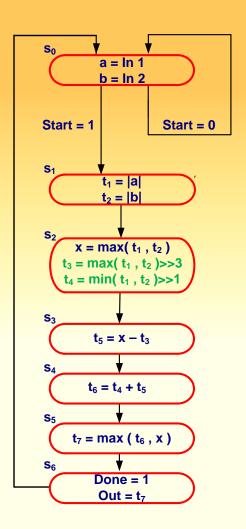

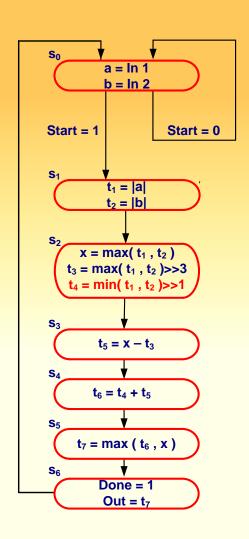

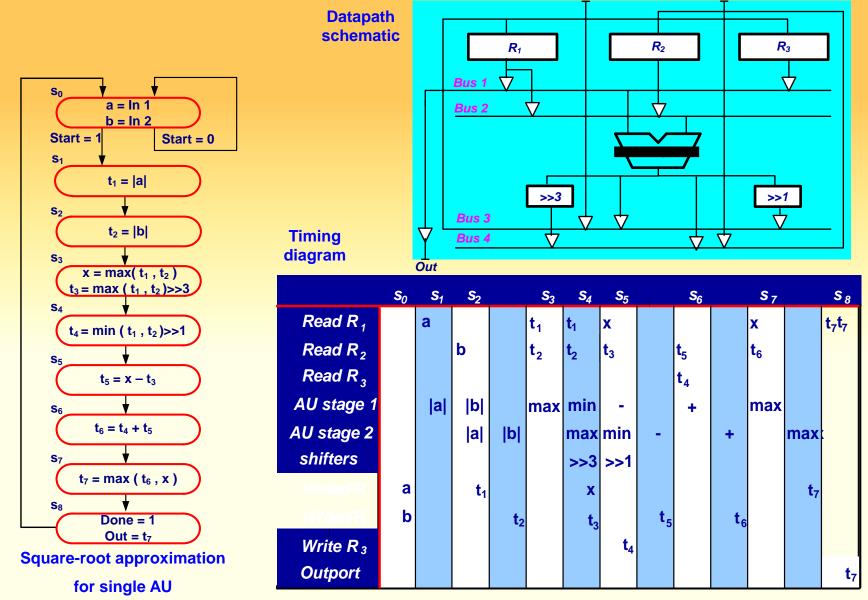

#### Square Root Approximation: C to CDFG

**Example:** Sq root (a + b) = max(0.875 x + 0.5 y), where x = max(|a|, |b|), y = min(|a|, |b|)

13

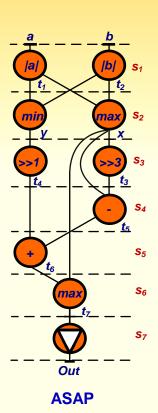

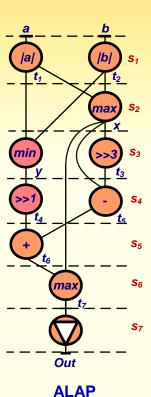

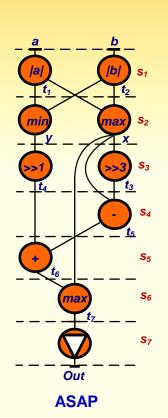

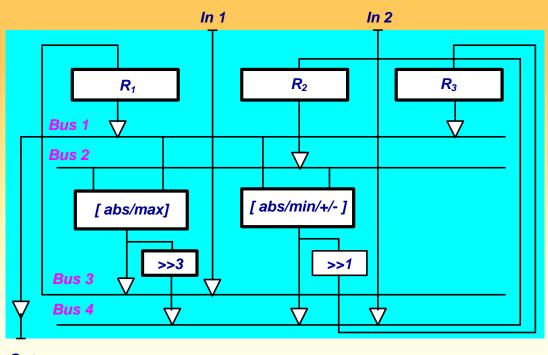

### Square Root Approximation: Scheduling

**Example:** Sq root (a + b) = max(0.875 x + 0.5 y), where x = max(|a|, |b|), y = min(|a|, |b|)

constrained Out

Resource-

14

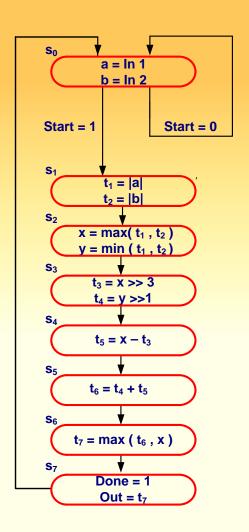

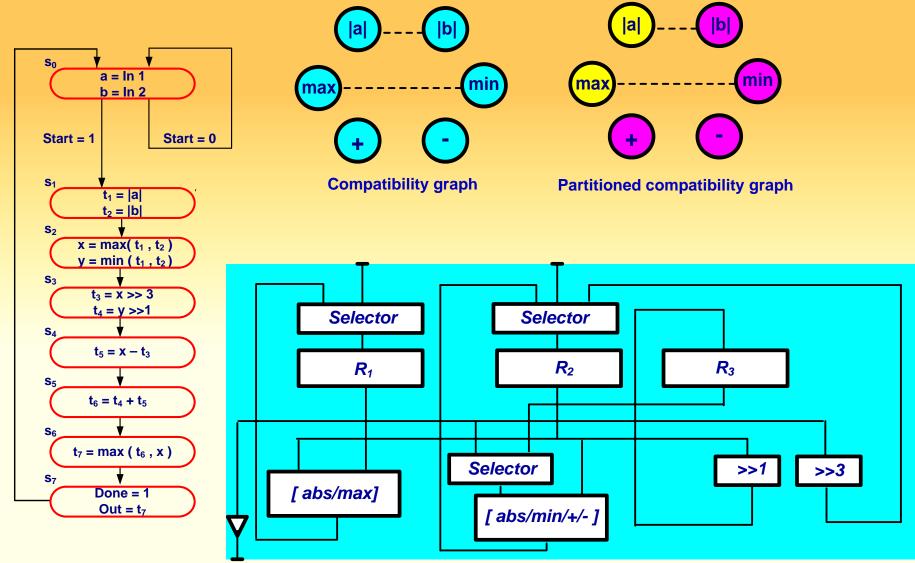

#### Square Root Approximation: CDFG to FSMD

Example: Sq root (a + b) = max(0.875 x + 0.5 y), where x = max(|a|, |b|), y = min(|a|, |b|)

Control/Data flow graph

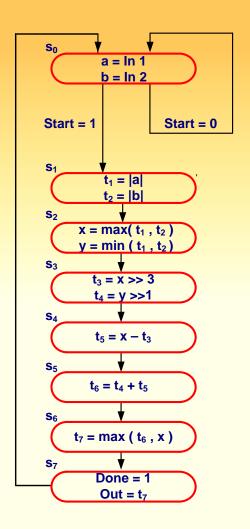

### Square Root Approximation: FSMD Design

**Example:** Sq root (a + b) = max(0.875 x + 0.5 y), where x = max(|a|, |b|), y = min(|a|, |b|)

- Storage allocation and sharing

- Functional unit allocation and sharing

- Bus allocation and sharing

### Resource usage in SRA

**Square-root approximation**

#### Variable usage

|                                  | s <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | S <sub>5</sub> | S <sub>6</sub> | s <sub>7</sub> |

|----------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| a                                | X              |                |                |                |                |                |                |

| b                                | X              |                |                |                |                |                |                |

| t <sub>1</sub>                   |                | X              |                |                |                |                |                |

| t <sub>2</sub>                   |                | X              |                |                |                |                |                |

| x                                |                |                | X              | X              | X              | X              |                |

| У                                |                |                | X              |                |                |                |                |

| t <sub>3</sub>                   |                |                |                | X              |                |                |                |

| t <sub>3</sub><br>t <sub>4</sub> |                |                |                | X              | X              |                |                |

| <b>t</b> <sub>5</sub>            |                |                |                |                | X              |                |                |

| t <sub>6</sub>                   |                |                |                |                |                | X              |                |

| t <sub>7</sub>                   |                |                |                |                |                |                | X              |

| No. of live variables            | 2              | 2              | 2              | 3              | 3              | 2              | 1              |

**Operation usage**

|   |                   | S <sub>1</sub> | S <sub>2</sub> | <b>S</b> <sub>3</sub> | S <sub>4</sub> | <b>S</b> <sub>5</sub> | S <sub>6</sub> | S <sub>7</sub> | Max. no.<br>of units |

|---|-------------------|----------------|----------------|-----------------------|----------------|-----------------------|----------------|----------------|----------------------|

| • | abs               | 2              |                |                       |                |                       |                |                | 2                    |

|   | min               |                | 1              |                       |                |                       |                |                | 1                    |

|   | max               |                | 1              |                       |                |                       | 1              |                | 1                    |

|   | >>                |                |                | 2                     |                |                       |                |                | 2                    |

|   | -                 |                |                |                       | 1              |                       |                |                | 1                    |

|   | +                 |                |                |                       |                | 1                     |                |                | 1                    |

|   | No. of operations | 2              | 2              | 2                     | 1              | 1                     | 1              |                |                      |

### Resource usage in SRA

**Connectivity usage**

**Square-root approximation**

**Operation usage**

|                   | S <sub>1</sub> | S <sub>2</sub> | <b>S</b> <sub>3</sub> | S <sub>4</sub> | <b>S</b> <sub>5</sub> | S <sub>6</sub> | S <sub>7</sub> | Max. no.<br>of units |

|-------------------|----------------|----------------|-----------------------|----------------|-----------------------|----------------|----------------|----------------------|

| abs               | 2              |                |                       |                |                       |                |                | 2                    |

| min               |                | 1              |                       |                |                       |                |                | 1                    |

| max               |                | 1              |                       |                |                       | 1              |                | 1                    |

| >>                |                |                | 2                     |                |                       |                |                | 2                    |

| -                 |                |                |                       | 1              |                       |                |                | 1                    |

| +                 |                |                |                       |                | 1                     |                |                | 1                    |

| No. of operations | 2              | 2              | 2                     | 1              | 1                     | 1              |                |                      |

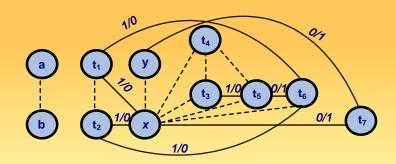

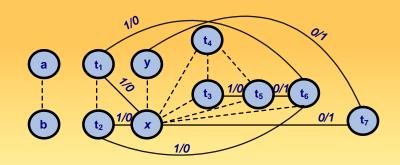

### Register sharing (Variable merging)

- Group variables with non-overlaping lifetimes

- Each group shares one register

- Grouping reduces number of registers needed in the design

- There are many partitioning algorithms

## Merging variables with common sources and destination

FSMD

**Datapath without register sharing**

**Datapath with register sharing**

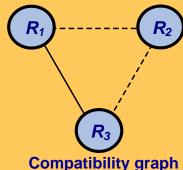

### Register sharing (Variable merging)

**Square-root approximation**

#### Compatibility graph

|                       | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | S <sub>5</sub> | S <sub>6</sub> | S <sub>7</sub> |

|-----------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| а                     | X              |                |                |                |                |                |                |

| b                     | X              |                |                |                |                |                |                |

| t <sub>1</sub>        |                | X              |                |                |                |                |                |

| t <sub>2</sub>        |                | X              |                |                |                |                |                |

| x                     |                |                | X              | X              | X              | X              |                |

| У                     |                |                | X              |                |                |                |                |

| t <sub>3</sub>        |                |                |                | X              |                |                |                |

| t <sub>4</sub>        |                |                |                | X              | X              |                |                |

| <b>t</b> <sub>5</sub> |                |                |                |                | X              |                |                |

| <b>t</b> <sub>6</sub> |                |                |                |                |                | X              |                |

| t <sub>7</sub>        |                |                |                |                |                |                | X              |

| No. of live           | 2              | 2              | 2              | 3              | 3              | 2              | 1              |

| variables             |                |                |                |                |                |                |                |

Variable usage

### Register sharing (Variable merging)

Partitioned compatibility graph

## a $t_1$ y $t_4$ 0.7 $t_5$ 0.7 $t_6$ 0.7 $t_7$ $t_8$ $t_8$

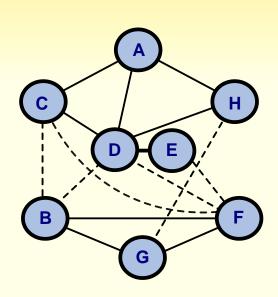

#### **Compatibility graph**

$$R1 = [a, t1, x, t7]$$

$R2 = [b, t2, y, t3, t5, t6]$   $R3 = [t4]$

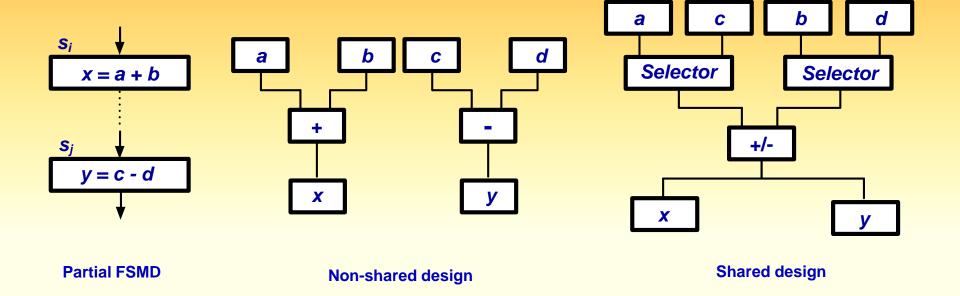

#### FU sharing (Operator merging)

- Group non-concurrent operations

- Each group shares one functional unit

- Sharing reduces number of functional units

- Grouping also reduces connectivity

- Clustering algorithms are used for grouping

### **FU-sharing motivation**

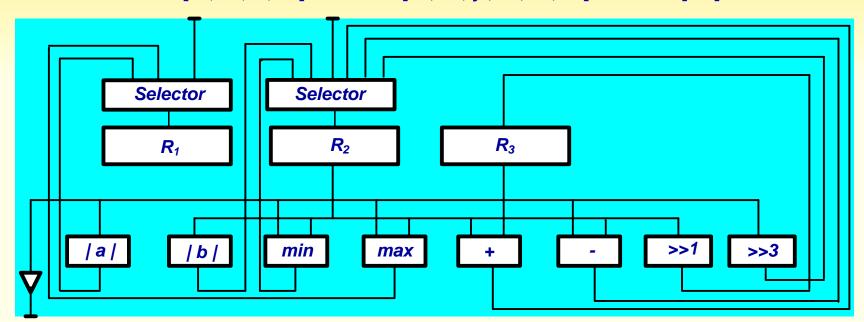

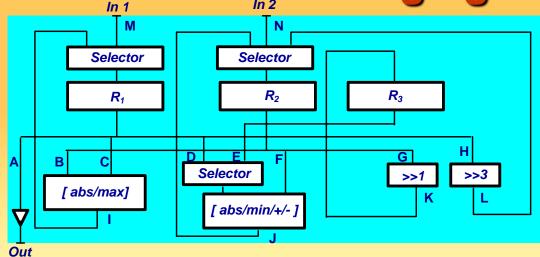

### Operator-merging for SRA

**Square-root approximation**

Datapath after variable and operator merging

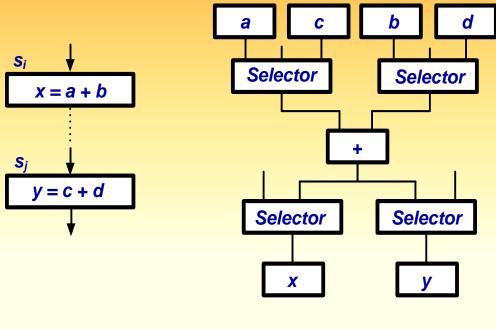

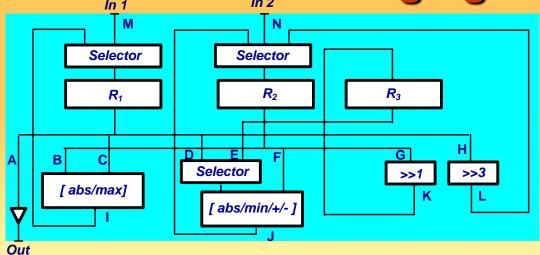

#### Bus sharing (connection merging)

- Group connections that are not used concurrently

- Each group forms a bus

- Connection merging reduces number of wires

- Clustering algorithm work well

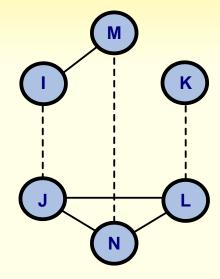

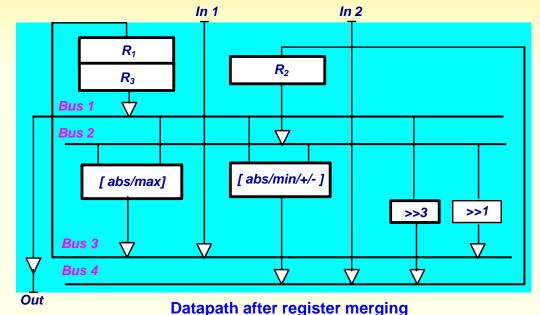

### Connection merging in SRA datapath

Datapath after variable and operator merging

- Bus1 = [ A, C, D, E, H ]

- Bus2 = [B, F, G]

- Bus3 = [ I, K, M ]

- Bus4 = [ J, L, N ]

**Bus assignment**

|   | Sn | S <sub>1</sub> | S <sub>2</sub> | <b>S</b> <sub>3</sub> | S₄ | S <sub>5</sub> | S <sub>6</sub> | S <sub>7</sub> |

|---|----|----------------|----------------|-----------------------|----|----------------|----------------|----------------|

| Α |    |                |                |                       |    |                |                | X              |

| В |    |                | X              |                       |    |                | X              |                |

| С |    | X              | X              |                       |    |                | X              |                |

| D |    |                | X              |                       | X  |                |                |                |

| Ε |    |                |                |                       |    | X              |                |                |

| F |    | X              | X              |                       | X  | X              |                |                |

| G |    |                |                | X                     |    |                |                |                |

| Н |    |                |                | X                     |    |                |                |                |

|   |    | X              | X              |                       |    |                | X              |                |

| J |    | X              | X              |                       | X  | X              |                |                |

| K |    |                |                | X<br>X                |    |                |                |                |

| L |    |                |                | X                     |    |                |                |                |

| M | X  |                |                |                       |    |                |                |                |

| N | X  |                |                |                       |    |                |                |                |

Connectivity usage table

Compatibility graph for input buses

Compatibility graph for output buses

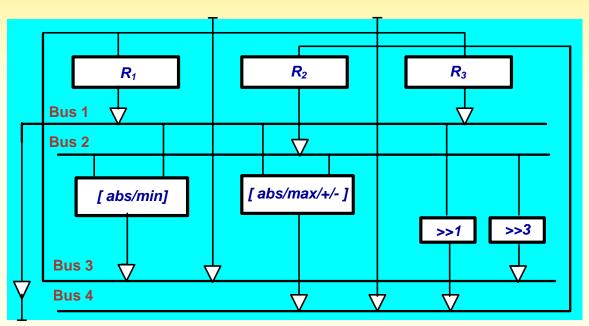

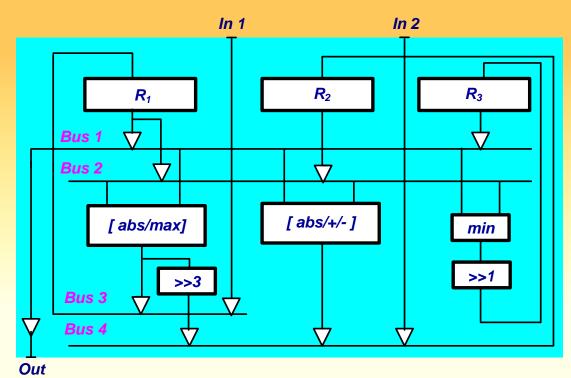

### Connection merging in SRA datapath

Datapath after variable and operator merging

- Bus1 = [ A, C, D, E, H ]

- Bus2 = [B, F, G]

- Bus3 = [ I, K, M ]

- Bus4 = [ J, L, N ]

**Bus assignment**

|        | So | S <sub>1</sub> | S <sub>2</sub> | <b>S</b> <sub>3</sub> | S₄ | S <sub>5</sub> | S <sub>6</sub> | S <sub>7</sub> |

|--------|----|----------------|----------------|-----------------------|----|----------------|----------------|----------------|

| Α      |    |                |                |                       |    |                |                | X              |

| В      |    |                | X              |                       |    |                | X              |                |

| С      |    | X              | X              |                       |    |                | X              |                |

| D      |    |                | X              |                       | X  |                |                |                |

| Ε      |    |                |                |                       |    | X              |                |                |

| E<br>F |    | X              | X              |                       | X  | X              |                |                |

| G      |    |                |                | X                     |    |                |                |                |

| Н      |    |                |                | X                     |    |                |                |                |

| - 1    |    | X              | X              |                       |    |                | X              |                |

| J      |    | X              | X              |                       | X  | X              |                |                |

| K      |    |                |                | X                     |    |                |                |                |

| L      |    |                |                | X                     |    |                |                |                |

| M      | X  |                |                |                       |    |                |                |                |

| N      | X  |                |                |                       |    |                |                |                |

Connectivity usage table

Datapath after variable, operator and connectivity merging

#### Register merging into Register files

- Group register with non-overlapping accesses

- Each group assigned to one register file

- Register grouping reduces number of ports, and therefore number of buses

- Use some clustering algorithms

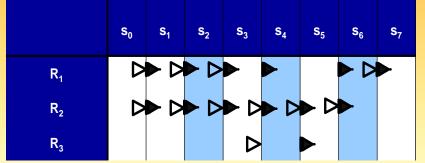

### Register merging

•

$$R_2 = [b, t_2, y, t_3, t_5, t_6]$$

•

$$R_3 = [t_4]$$

**Register assignment**

Register access table

**Square-root approximation**

a = ln 1

b = ln 2

t₁ = |a|  $t_2 = |b|$

$x = max(t_1, t_2)$

$y = min(t_1, t_2)$

$t_3 = x >> 3$  $t_4 = y >> 1$

$\mathbf{t}_5 = \mathbf{x} - \mathbf{t}_3$

$\mathbf{t}_6 = \mathbf{t}_4 + \mathbf{t}_5$

$t_7 = max(t_6, x)$

Done = 1 Out =  $t_7$

Start = 0

Start = 1

$S_2$

$S_3$

**S**<sub>5</sub>

**S**<sub>7</sub>

### Chaining and multi-cycling

- Chaining allows serial execution of two or more operations in each state

- Chaining reduces number of states and increases performance

- Multi-cycling allows one operation to be executed over two or more clock cycles

- Multi-cycling reduces size of functional units

- Multi-cycling is used on noncritical paths to improve resource utilization

#### SRA datapath with chained units

Out

#### **Datapath schematic**

•

$$R_1 = [a, t_1, x, t_7]$$

•

$$R_2 = [b, t_2, y, t_3, t_5, t_6]$$

•

$$R_3 = [t_4]$$

**Square-root approximation**

#### SRA datapath with multi-cycle units

**Square-root approximation**

**Datapath schematic**

•

$$R_1 = [a, t_1, x, t_7]$$

•

$$R_2 = [b, t_2, y, t_3, t_5, t_6]$$

•

$$R_3 = [t_4]$$

### **Pipelining**

- Pipelining improves performance at a very small additional cost

- Pipelining divides design into stages and uses all stages concurrently for different data (assembly line principle)

- Pipelining principles works on several levels:

- (a) Unit pipelining

- (b) Control pipelining

- (c) Datapath pipelining

### SRA datapath with single AU

In 2

### Pipelined FSMD implementation

Standard FSMD implementation

### Summary

#### We introduced RTL design:

- FSMD model

- RTL specification with

- >FSMD

- **≻CDFG**

- Procedure for synthesis from RTL specification

- Scheduling of basic blocks

- Design Optimization through

- ▶ Register sharing

- Functional unit sharing

- **≻Bus sharing**

- ➤Unit chaining

- **≻**Multi-clocking

- Design Pipelining

- **≻Unit pipelining**

- **≻**Control pipelining

- > Datapath pipelining