# System-on-Chip Environment (SCE Version 2.2.0 Beta): Manual

Lukai Cai Andreas Gerstlauer Samar Abdi Jerry Peng Dongwan Shin Haobo Yu Rainer Dömer Daniel D. Gajski

Technical Report CECS-TR-03-45 December 2003

## System-on-Chip Environment (SCE Version 2.2.0 Beta): Manual

Lukai Cai Andreas Gerstlauer Samar Abdi Jerry Peng Dongwan Shin Haobo Yu Rainer Dömer Daniel D. Gajski

Technical Report CECS-TR-03-45 December, 2003

Center for Embedded Computer Systems University of California, Irvine Irvine, CA 92697-3425, USA +1 (949) 824-8919

http://www.cecs.uci.edu

# Contents

| 1 | Intro | oduction | n                     | 1    |

|---|-------|----------|-----------------------|------|

| 2 | Ove   | rview    |                       | 3    |

|   | 2.1   | Modul    | les                   | . 4  |

|   |       | 2.1.1    | Main Window           | . 6  |

|   |       | 2.1.2    | Input Dialogs         | . 6  |

|   |       | 2.1.3    | Display Windows       | . 7  |

|   | 2.2   | Requir   | rements               | . 7  |

|   | 2.3   | Interfa  | aces                  | . 8  |

|   |       | 2.3.1    | Internal Interfaces   | . 8  |

|   |       | 2.3.2    | External Interfaces   | . 8  |

|   | 2.4   | Perform  | mance                 | . 9  |

| 3 | Win   | dows/G   |                       | 9    |

| 5 | 3.1   | Menu 1   |                       |      |

|   | 5.1   | 3.1.1    | File Menu   File Menu |      |

|   |       | 3.1.2    | Edit Menu             |      |

|   |       | 3.1.3    | View Menu             |      |

|   |       | 3.1.4    | Project Menu          |      |

|   |       | 3.1.5    | Synthesis Menu        |      |

|   |       | 3.1.6    | Validation Menu       |      |

|   |       | 3.1.7    | Windows               |      |

|   | 3.2   | Project  | t Window              | . 14 |

|   |       | 3.2.1    | Models Tab            | . 16 |

|   |       | 3.2.2    | Imports Tab           | . 16 |

|   |       | 3.2.3    | Sources Tab           | . 17 |

|   | 3.3   | Design   | n Window              | . 19 |

|   |       | 3.3.1    | Hierarchy Tab         | . 19 |

|   |       | 3.3.2    | Behaviors Tab         | . 20 |

|   |       | 3.3.3    | Channels Tab          | . 21 |

|   |       | 3.3.4    | View Pane             | . 21 |

|   | 3.4   | Output   | t Window              | . 22 |

|   | 3.5   |          | space                 | . 23 |

|   | 3.6   | -        | ge Boxes              | . 23 |

|   |       | 3.6.1    | Error Dialogs         | . 23 |

|   |       | 3.6.2    | Information Dialogs   | . 24 |

|   |       |          |                       |      |

| 4  | Fun   | ctionali | ty 2                                    | 24 |

|----|-------|----------|-----------------------------------------|----|

|    | 4.1   | Applic   | ation                                   | 25 |

|    |       | 4.1.1    | Preferences Editing                     | 26 |

|    | 4.2   | Project  | t Handling                              | 28 |

|    |       | 4.2.1    | Project Creation                        | 31 |

|    |       | 4.2.2    | Project Opening 3                       | 31 |

|    |       | 4.2.3    | 5 0                                     | 32 |

|    |       | 4.2.4    | , , , , , , , , , , , , , , , , , , , , | 33 |

|    |       | 4.2.5    | 6 6                                     | 34 |

|    |       | 4.2.6    | Design Opening 3                        | 35 |

|    |       | 4.2.7    | 6                                       | 35 |

|    |       | 4.2.8    | 6 6                                     | 35 |

|    |       | 4.2.9    |                                         | 86 |

|    |       | 4.2.10   | 5 8                                     | 86 |

|    | 4.3   |          | 6                                       | 86 |

|    |       | 4.3.1    |                                         | 37 |

|    |       | 4.3.2    | 6                                       | 38 |

|    |       | 4.3.3    | 6                                       | 39 |

|    |       | 4.3.4    | 1                                       | 40 |

|    |       | 4.3.5    | 8 1 2 8                                 | 11 |

|    |       | 4.3.6    | 6                                       | 11 |

|    | 4.4   | •        | 5 8                                     | 12 |

|    |       | 4.4.1    |                                         | 12 |

|    |       | 4.4.2    | 5 51 8                                  | 13 |

|    |       | 4.4.3    | 5                                       | 13 |

|    |       | 4.4.4    |                                         | 14 |

|    | 4.5   | Synthe   |                                         | 14 |

|    |       | 4.5.1    | 5                                       | 14 |

|    |       | 4.5.2    | 5                                       | 53 |

|    |       | 4.5.3    | 1                                       | 59 |

|    | 4.6   | Windo    | w Management                            | 50 |

| Re | feren | ces      | 6                                       | 53 |

| A  | Man   | ual Pag  | res f                                   | 54 |

|    | A.1   |          |                                         | 55 |

# List of Figures

| 1  | System-on-Chip Environment                   |

|----|----------------------------------------------|

| 2  | Overview of the software architecture of SCE |

| 3  | Module diagram of SCE                        |

| 4  | Main Window of SCE                           |

| 5  | Project Window (Models tab)                  |

| 6  | Project Window (Imports tab)                 |

| 7  | Project Window (Sources tab) 18              |

| 8  | Design Window (Hierarchy tab)                |

| 9  | Design Window (Behaviors tab)                |

| 10 | Design Window (Channels tab)                 |

| 11 | Output Window                                |

| 12 | Error dialog                                 |

| 13 | Information dialog                           |

| 14 | Edit Preferences dialog (Compiler tab)       |

| 15 | Edit Preferences dialog (Database tab)       |

| 16 | Database Selection dialog                    |

| 17 | Project Open dialog                          |

| 18 | Project Save dialog                          |

| 19 | Project Settings dialog                      |

| 20 | File Open dialog                             |

| 21 | File Save dialog                             |

| 22 | File Importing dialog                        |

| 23 | Design Property dialog                       |

| 24 | PE Allocation dialog                         |

| 25 | PE Selection dialog                          |

| 26 | Architecture Refinement dialog               |

| 27 | Bus Allocation dialog                        |

| 28 | Bus Selection dialog                         |

| 29 | Communication Refinement dialog              |

| 30 | Import Decisions dialog                      |

## System-on-Chip Environment (SCE Version 2.2.0 Beta): Manual

L. Cai, A. Gerstlauer, S. Abdi, J. Peng, D. Shin, H. Yu, R. Dömer, D. Gajski

Center for Embedded Computer Systems University of California, Irvine

Technical Report CECS-TR-03-45 December, 2003

## **1** Introduction

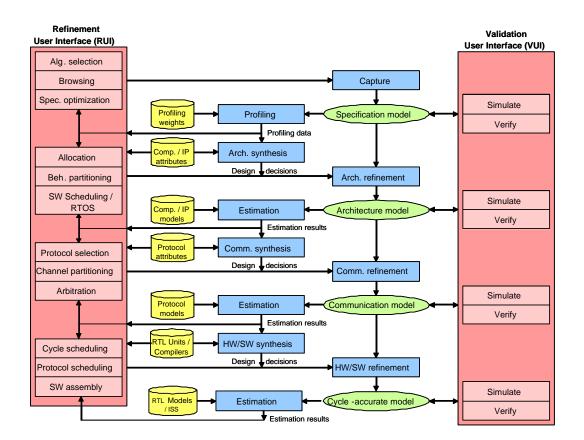

The SCE provides an environment for modeling, synthesis and validation. It includes a graphical user interface (GUI) and a set of tools to facilitate the design flow and perform the aforementioned refinement steps. The two major components of the GUI are the Refinement User Interface (RUI) on the left and the Validation User Interface (VUI) on the right as shown in Figure 1. The RUI allows designers to make and input design decisions, such as component allocation, specification mapping. With design decisions made, refinement tools can be invoked inside RUI to refine models. The VUI allows the simulation of all models to validate the design at each stage of the design flow. Each of the boxes corresponds to a tool which performs a specific task automatically. A profiling tool is used to obtain the characteristics of the initial specification, which serves as the basis for architecture synthesis. The refinement tool set automatically transforms models based on relevant design decisions. The estimation tool set produces quality metrics for each intermediate models, which can be evaluated by designers. With the assistance of the GUI and tool set, it is relatively easy for designer to step through the design process. With the editing, browsing and algorithm selection capability provided by RUI, a specification model can be efficiently captured by designers. Based on the information profiled on the specification, designers input architectural decisions and apply the architecture refinement tool to derive the architecture model. If the estimated metrics are satisfactory, designers can focus on communication issues, such as protocol selection and channel partitioning. With communication decisions made, the communication refinement tool is used to generate the communication model. Finally, the implementation model is produced in the similar fashion. The implementation model is ready for RTL synthesis. We are currently in the process of developing tools for automating the synthesis tasks for system level design shown in the exploration engine. The manual concentrates on automatic synthesis process.

Figure 1: System-on-Chip Environment.

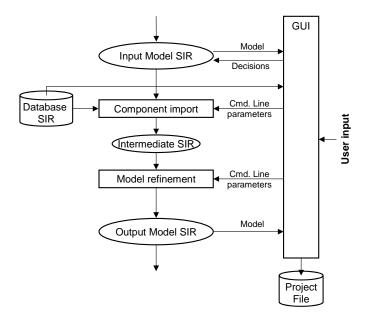

Figure 2: Overview of the software architecture of SCE.

## 2 Overview

Figure 2 shows an overview of the software architecture of each synthesis step of SCE. Each step requires an input model of the intended design in the form of valid SpecC code [1]. For example, the input model is the specification model for the architecture refinement, the architecture model for communication refinement.

Architecture synthesis reads information about available components from a database of processing elements (PEs). Communication synthesis reads information about available components from databases of buses. The database is read in binary form as a file in SpecC Internal Representation (SIR) format. Through SCE's graphical user interface (GUI), the user can browse the specification/architecture/communication model and PE/bus database, and the user is provided with a GUI to enter design decisions to come up with different design decisions. For architecture synthesis, the decisions are computation architectures and mappings of the specification onto those architectures. For communication synthesis,

the decisions are communication architecture and mappings of the channels to buses.

For each candidate design decision as determined by the user, each step automatically generates an output model that exactly reflects the design decisions made. The output model is the architecture model for architecture synthesis, and the communication model for communication synthesis.

Information about design models and their relationships are tracked by the SCE and can be stored in project files that can be read and written by SCE in a custom XML format. Generated architecture models along with the corresponding project file(s) can then be passed to the following tools in the SCE design flow.

Internally, the SCE consists of separate components for component import, architecture/communication refinement, and graphical user interface (GUI). The main SCE application is the SCE GUI which in turn calls import and refinement components as needed. Component import and refinement are command line tools that are called and executed by the GUI where the GUI supplies the correct command line parameters, captures the output and handles (normal or abnormal) results. The GUI reads and displays design models, lets the user browse the database, and provides facilities to enter design decisions. Design decisions are stored by the GUI as annotations in the input design model. For generation of output design models, the GUI first passes the annotated design to the component import tool which, as requested by the GUI, imports the necessary component models out of the database into the design and writes an intermediate design model. The GUI then calls the refinement tool on the intermediate design model. The refinement tool in turn generates the final output architecture model which can be read, displayed and browsed through the GUI.

The run time of automatic model generation is in the order of minutes. Therefore with SCE, users can rapidly experiment with dozens, even hundreds of alternative design decisions to make the optimal design decisions.

#### 2.1 Modules

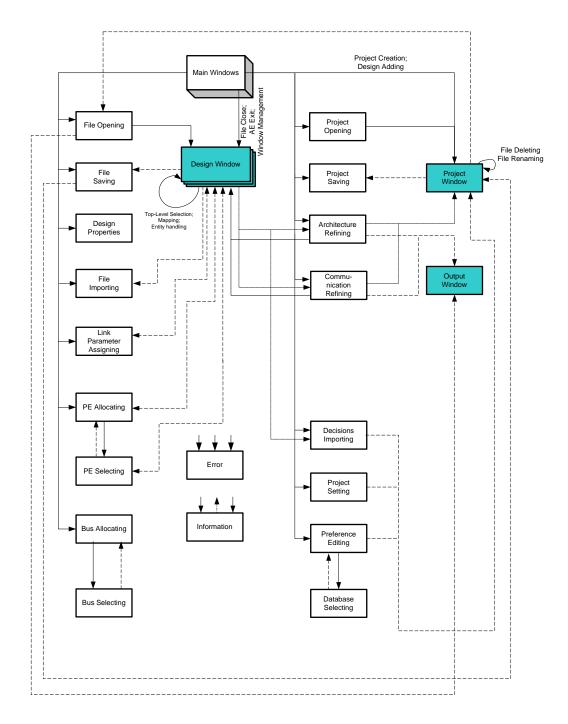

The block diagram and flow chart of the SCE is displayed in Figure 3. The blocks represent SCE modules where each block is associated with one or more GUI elements. GUI elements and hence SCE blocks can be further classified into three types: the Main Window, input dialogs and display windows.

Besides above three types of windows, there are two types of arrows in Figure 3: solid arrows and dashed arrows. Solid arrows represent the pop-up relations. The window at the arrow head will be triggered by clicking a button or selecting a menu item in the window at the arrow tail. For example, by clicking *Open* button in *File* column in the menu of window Main Window, users will trigger *File Open* dialog. The text that appears on some arrows represents the arrow's task name. On the other hand, dashed arrows represent information updates. The data in the window at the arrow head will be updated by clicking a button in the window at the arrow tail. In order to simplify Figure 3, the arrows for error and

Figure 3: Module diagram of SCE.

information dialogs are not connected. They are popped up when the error or information occurs, which will be described in Section 4.

#### 2.1.1 Main Window

The main window (shown as 3-D block in Figure 3), is the default, top-level window of the GUI and hence the SCE application. The main window contains a menu bar and a status bar through which the application can be controlled by the user and through which feedback is provided to the user about the state of the application.

#### 2.1.2 Input Dialogs

Input dialogs (shown as regular blocks) allow users to input the design or project decisions by selecting, editing, or typing the details. They are all pop-up dialogs. Users directly/indirectly pop up all the input dialogs by clicking buttons or selecting menu items. Input dialogs include:

- (a) File Open dialog for selecting the design file which users want to open.

- (b) File Save dialog for saving current file as a new file with the specified name.

- (c) Design Property dialog for displaying the information related to the process of SCE, such as command history and processing status of SCE.

- (d) File Import dialog for selecting the design file which users want to import.

- (e) PE Allocation dialog for adding PEs to and removing PEs from the design.

- (f) PE Selection dialog for selecting PEs from the PE library (for input dialog PE Allocating).

- (g) Bus Allocation dialog for adding busses to and removing busses from the design.

- (h) Bus Selecting dialog for selecting busses from the bus database.

- (i) Error dialogs for displaying of error messages of design tasks.

- (j) Information dialogs for providing informational feedback to the user.

- (k) Project Open dialog for reading a new project from disk.

- (1) Project Save dialog for saving current project as a new project on disk with the specified name.

- (m) Architecture Refinement dialog for selecting sub-tasks for architecture refinement.

- (n) Communication Refinement dialog for selecting sub-tasks for communication refinement.

- (o) Decision Import dialog for import the design decisions from other opened designs.

- (p) Project Settings dialog for setting project preferences.

- (q) Edit Preferences dialog for setting SCE preferences.

- (r) Database Selection dialog for selecting the preferred database.

#### 2.1.3 Display Windows

Display windows (shown as shaded windows in Figure 3) graphically display the information of files, projects, and the process status of SCE. Display windows are sub-windows under the main window. Display windows include:

- (a) Design Window displays the contents and the attributes of the designs saved in the opened files. The displayed information includes hierarchy of behaviors, execution sequence of behaviors, and variable/port details of the selected behavior.

- (b) Project Window displays the project information such as hierarchy of design models and included source files.

- (c) Output Window displays the captured output of the SCE command line tools called by the GUI.

#### 2.2 Requirements

The SCE requires a system with the following runtime platform:

Host machine Intel-compatible x86 PC, 500MHz or higher, recommended minimum 128MB of RAM, 200MB of free hard disk space.

**Operating system** RedHat Enterprise Linux WS, Version 3

In order to compile the source code of SCE, the following additional software packages have to be installed (in binary form including necessary header files):

- SIR library, Version 2.2.x (UC Irvine)

- Qt library and toolkit, Version 3.3.x (Trolltech, Inc.)

- PyQt library, Version 3.11 or higher (Riverbank Computing, Ltd.)

Note that in order to redistribute the libraries together with the compiled SCE, commercial licenses of the above tools have to be obtained as necessary.

### 2.3 Interfaces

SCE interfaces can be separated into internal interfaces for information exchange between SCE components and external interfaces for information exchange with other tools both within SCE and outside of SCE.

#### 2.3.1 Internal Interfaces

Components inside SCE exchange information through design models, command line parameters, logging output, and exit codes.

- **Design models** Design models are exchanged between SCE components in the form of SpecC files stored on any file system supported by the underlying operating system (Linux). In addition to the SpecC code for the design models themselves, SCE components exchange information via annotations for design decisions and design meta-information.

- **Command line parameters** When calling command line tools, the SCE GUI will pass information for controlling the tool in the form of command line parameters.

- **Logging output** Command line tools will produce logging output during execution. This logging output is captured by the GUI and displayed to the user in the GUI's output window.

- **Exit codes** Command line tools signal status information (success or error codes in the case of tool failure) to the GUI in the form of their exit codes. The GUI analyzes command line tool exit codes and translates them into necessary information or error messages.

#### 2.3.2 External Interfaces

The SCE exchanges information with other tools and with the designer via design models, databases, project files and via SCE's graphical user interface:

**Design models** Design models are exchanged between SCE's tools in the form of SpecC source code stored as files in any file system supported by the underlying operating system (Linux). SpecC source files are stored as text files in DOS or Unix end-of-line format where SCE will be able to read both formats and to export files in DOS form. Generally, SpecC source code is stored in plain ASCII format. However, SCE will be able to transparently handle Kanji-encoded comments and strings.

SCE will generally be able to import any valid SpecC code that is parsable according to the syntax and grammar of SpecC 2.0 (based on standard ANSI C) as defined in

the SpecC Language Reference Manual (LRM), Version 2.0 [1]. Note that inside SCE no object code or executables are ever created and therefore models imported into SCE can include foreign code that depends on libraries outside (i.e. does not have to be linkable on) the underlying host platform (Linux). In contrast, since SCE will preprocess the SpecC source files on the host platform and inline any included code in its exported models, pre-prepared, clean header files with all specific code to be included have to be supplied together with the SCE import SpecC models as necessary for external tools.

In addition, individual models imported into SCE will have to conform to the specific rules and guidelines defined in the specification documents for each type of model.

- **Databases** Databases are generated by the library builder and stored as a collection of binary SpecC Internal Representation (SIR) files managed via a specific file system hierarchy on top of the general underlying file system. SCE components then read component models from these SIR database files.

- **Project files** Project files are stored as XML files in any file system supported by the underlying operating system (Linux). Project XML files are text files using Unix text file format. Project files use a custom XML format that is common to all tools in the SCE environment, i.e. the project XML file format is shared among the SCE tools and any SCE tool is able to read, write and modify project files generated by or used as input to any other SCE tool.

- **User interface** All user input is entered in SCE through a graphical user interface (GUI). The SCE GUI is built on top of the X11 windowing system and as such can be run on any local or remote X window server.

#### 2.4 Performance

The SCE will guarantee that for a typical design with less than 10,000 lines of code, less than 10 PEs, and less than 100 behaviors, variables and channels, automatic generation of the refined model will take less than 5 minutes.

## 3 Windows/GUI

The primary GUI of SCE is the Main Window, which is displayed in Figure 4. The Main Window consists of six parts:

(a) A Menu Bar that contains several columns of commands. Each column is a drop-down menu (see Section 3.1).

| SoC Environment                                            | <b>. .</b> × |

|------------------------------------------------------------|--------------|

| <u>Eile Edit View Project Synthesis Validation Windows</u> | <u>H</u> elp |

| D 🛩   ■ ■   <i>●</i>   ♥ ♥   ೫ 🐚   ೫    ± 💷    ●           |              |

| Models Imports Sources                                     |              |

| Compile Simulate Analyze Refine Synthesize Shell           |              |

| Ready                                                      |              |

Figure 4: Main Window of SCE.

- (b) A Tool Bar that contains a list of short-cut icons. Each icon represents a command in the menu bar.

- (c) A Project Window (see Section 3.2).

- (d) A Workspace that contains a number of opened Design Windows (see Section 3.3).

- (e) An Output Window (see Section 3.4).

- (f) A Status Bar that displays the current status of SCE, such as "Loading..." or "Ready".

In this section, we introduce organization-related and display-related details of Menu Bar, Project Window, Display Windows, and Output Window. Some windows contain dropdown menus or pop-up menus. The menus further contain design commands. The usage and functionality behind the commands will be described later in Section 4.

#### 3.1 Menu Bar

The Menu Bar contains seven main menu entries: *File, Edit, View, Project, Synthesis, Validation,* and *Windows.* Each main menu entry is a drop-down menu which contains a number of commands. In general, unless otherwise noted, selecting a main menu entry will apply the corresponding action to the currently active design, i.e. to the design window in the workspace that currently has the input focus. If there is no currently active design window, menu commands will silently fail (do nothing).

#### 3.1.1 File Menu

The File menu contains eight commands:

- *Open* Selecting *Open* will allow loading and opening of an existing design file (see Section 4.3.1).

- *Close* Selecting *Close* will close the currently active design (see Section 4.3.3).

- Save Selecting Save will save the currently active design file (see Section 4.3.2).

- *Save As* Selecting *Save As* will save the currently active design as a new file (see Section 4.3.2).

- Save All Selecting Save All will save all the opened files (see Section 4.3.2).

- *Import* Selecting *Import* will import a design file into the currently active design (see Section 4.3.4).

- *Properties* Selecting *Properties* will display the properties of the currently active design (see Section 4.3.5).

- *Exit* Selecting *Exit* will exit from and quit SCE (see Section 4.3.6).

#### 3.1.2 Edit Menu

- The *Edit* menu contains six commands:

- Undo Selecting Undo will undo the previous action.

- *Redo* Selecting *Redo* will redo the previous action.

- Cut Selecting Cut will cut the selected text and save it in the buffer.

- Copy Selecting Copy will copy the selected text and save it in the buffer.

- *Paste* Selecting *Paste* will paste the content in the buffer to the place where the mouse points to.

- *Preferences* Selecting *Preferences* will allow viewing and modifying of application preferences (see Section 4.1.1).

#### 3.1.3 View Menu

The View menu contains four commands:

- *Source* Selecting *Source* will display the source file of the selected design.

- Graph Selecting Graph will display profiling graphes of the selected design.

- *Connectivity* Selecting *Connectivity* will display the connectivity of behaviors of the selected design.

*Hierarchy* Selecting *Hierarchy* will display the behavior hierarchy graphically.

#### 3.1.4 Project Menu

The *Project* menu contains seven commands:

New Selecting New will create a new project and open it (see Section 4.2.1).

**Open** Selecting Open will open an existing project file (see Section 4.2.2).

*Close* Selecting *Close* will close the current project (see Section 4.2.10).

Save Selecting Save will save the current project file (see Section 4.2.3).

- Save As Selecting Save As will save the current project as a new project file (see Section 4.2.3).

- Add Design Selecting Add Design will add the current design into the project.

- *Settings* Selecting *Settings* will allow viewing and modifying of project settings (see Section 4.2.4).

#### 3.1.5 Synthesis Menu

The Synthesis menu contains following commands:

- *Show Variables* Selecting *Show Variables* will toggle displaying of variables in the currently active design window (see Section 4.4.4).

- *Show Channels* Selecting *Show Channels* will toggle displaying of channels in the currently active design window. (see Section 4.4.4)

- *Allocate PE* Selecting *Allocate PE* will allow allocation and selection of PEs/memories from the PE database (see Section 4.5.1).

- *Allocate Busses* Selecting *Allocate Busses* will allow users to allocate busses from the bus database. (see Section 4.5.2).

- *Import Decisions* Selecting *Import Design* will allow importing of design decisions from another opened design (see Section 4.5.3).

- *Architecture Refinement* Selecting *Architecture Refinement* will perform architecture refinement to generate the refined architecture model (see Section 4.5.1).

- *Communication Refinement* Selecting *Communication Refinement* will perform communication refinement to generate the communication model (see Section 4.5.2).

#### 3.1.6 Validation Menu

The Validation menu contains four commands:

*Compile* Selecting *Compile* will compile the current design.

*Simulate* Selecting *Simulate* will simulate the current design.

*Profile* Selecting *Profile* will profile the current design.

*Estimate* Selecting *Estimate* will estimate the current design.

#### 3.1.7 Windows

The Windows menu contains six commands:

- Close Selecting Close will close the currently active design window in the Workspace.

- Close All Selecting Close All will close all design windows in the Workspace.

- *Next* Selecting *Next* will switch focus to and raise the next design window in the Workspace.

- *Previous* Selecting *Previous* will switch focus to and raise the previous design window in the Workspace.

- *Tile* Selecting *Tile* will rearrange the design windows in the Workspace in a tiled style.

- *Cascade* Selecting *Cascade* will rearrange the design windows in the Workspace in a cascaded style.

- *Project Manager* Selecting/unselecting *Project Manager* will display or undisplay the Project Window.

- *Output Window* Selecting/unselecting *Output Window* will display or undisplay the Output Window.

At the bottom of the *Windows* menu, the names of all opened design windows will be listed. Selecting the name of a design will switch focus to and raise (bring to the front) the corresponding design window.

Details about the usage and functionality of these commands are introduced in Section 4.6.

#### 3.2 Project Window

The Project Window is a sub-window of the Main Window, displaying project information. In general, a project holds meta-information about a set of design files and their relationship, e.g. a parent-child relationship in case a design was generated from another design through refinement. Hence, each file represents a design of the project at one abstraction level. In addition, the project can hold project-specific settings for the design environment, such as the compiling and parsing environment (paths).

At any time, the SCE application can keep one project open and active in memory. The name of this currently active project is displayed in the title bar of the Main Window. The Project Window displays the hierarchical information of design files in the currently active project. If there is no active project, the Project Window is disabled.

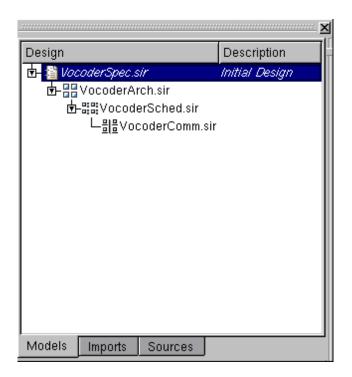

Figure 5: Project Window (Models tab).

The Project Window can be detached or docked. Users can drag the window (by its title bar or handle) to the desired place. If the Project Window is detached, it can be floating and displayed anywhere on the desktop. If the Project Window is docked, it has to be attached to any of the borders of the Main Window.

The Project Window contains three tabs: *Models*, *Imports*, and *Sources*. By clicking the tab at the bottom of the window, the corresponding tab will be activated and brought to the front.

#### 3.2.1 Models Tab

Figure 5 shows the screenshot of the Models tab. The Models tab contains two columns. Column *Design* displays the name of each design file in the project. If one design is derived or generated from another, the derived design is displayed as the child design of the previous one. The derivation hierarchy is indicated through connecting lines of a tree structure.

Users can select a design by clicking the row in which the design is displayed. Doubleclicking on a row will open the corresponding design. If the design is currently opened and loaded, double-clicking will activate (switch focus to and raise to the front) the corresponding design window in the Workspace (see Section 3.5).

The Column *Description* shows an optional description of the design. By clicking into the column, the user can edit the description text of the selected design directly in the corresponding table cell.

Right-clicking on a row will open a context menu pop-up for the selected design. The context menu contains four commands:

- *Open* Selecting *Open* will open the selected file (see Section 4.3.1). If the selected design is already opened, the corresponding design window in the workspace will be activated.

- **Delete** Selecting *Delete* will remove the selected file from the project and optionally delete the file on disk (see Section 4.2.7).

**Rename** Selecting *Rename* will rename the selected file (see Section 4.2.8).

*Change Description Change Description* will trigger editing of the description of the selected file. (see Section 4.2.9)

Note that renaming and changing of description actions can also be triggered by clicking into the corresponding column of the selected file.

#### 3.2.2 Imports Tab

Figure 6 shows the screenshot of Imports tab. The Imports tab displays a lists of imported design names. The list contains the union of all the sub-designs that have been imported directly or indirectly into any of the design files that are part of the project.

Users can select an imported design by clicking the row in which the imported design is displayed. Double-clicking on an imported design opens the corresponding design in the workspace.

Right-clicking on an imported design opens a context-menu pop-up for the selected design. The context menu contains one command:

Open Selecting Open will open the import design file (see Section 4.3.1).

Note that the opening action is equivalent to double-clicking on the imported design.

| Design 4               |  |  |  |  |

|------------------------|--|--|--|--|

| alu_32                 |  |  |  |  |

| arg_handler            |  |  |  |  |

| array_op 🚽             |  |  |  |  |

| autocorr               |  |  |  |  |

| az_lsp                 |  |  |  |  |

| basic_func             |  |  |  |  |

| basic_op               |  |  |  |  |

| build_cn_code          |  |  |  |  |

| build_code             |  |  |  |  |

| c_double_handshake     |  |  |  |  |

| closed_loop            |  |  |  |  |

| cn_encoding            |  |  |  |  |

| cod_12k2               |  |  |  |  |

| code_10i40_35bits      |  |  |  |  |

| codebook 🛛             |  |  |  |  |

| codebook_cn            |  |  |  |  |

| coder 🔽                |  |  |  |  |

| Models Imports Sources |  |  |  |  |

Figure 6: Project Window (Imports tab).

#### 3.2.3 Sources Tab

Figure 7 shows the screenshot of Sources tab. The Sources tab displays a lists of names of source files. The list contains the union of all SpecC source files that are sources for the design files that are part of the project.

The Sources tab does not allow any action on the files and is for informative purposes only.

|                    |             | <u> </u> |  |  |  |

|--------------------|-------------|----------|--|--|--|

| File               |             | A        |  |  |  |

| alloca.h           |             |          |  |  |  |

| alu.sc             |             |          |  |  |  |

| arg_handler.sc     |             |          |  |  |  |

| array_op.sc        |             |          |  |  |  |

| assert.h           |             |          |  |  |  |

| autocorr.sc        |             |          |  |  |  |

| az_lsp.sc          |             |          |  |  |  |

| basic_func.sc      |             |          |  |  |  |

| basic_op.sc        | basic_op.sc |          |  |  |  |

| build_cn_code.sc   |             |          |  |  |  |

| build_code.sc      |             |          |  |  |  |

| c_double_handshal  | (e.sc       |          |  |  |  |

| closed_loop.sc     |             |          |  |  |  |

| cn_encoding.sc     |             |          |  |  |  |

| cod_12k2.sc        |             |          |  |  |  |

| code_10i40_35bits. | SC          |          |  |  |  |

| codebook_cn.sc     | -           |          |  |  |  |

| Models Imports     | Sources     | J        |  |  |  |

Figure 7: Project Window (Sources tab)

#### **3.3 Design Window**

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Туре                                                                      | PE  | Bus | Name                                                                                                       | Туре                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----|-----|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Main         Image: Coder         Image: Coder_Incess         Image: Coder_Incess | Coder<br>Pre_Process<br>Coder_12k2<br>Post_Process<br>Monitor<br>Stimulus | DSP |     | G serial_bits     G serial_bits     G speech_sar     G txdtx_ctrl     S coder     S monitor     S stimulus | ode bool<br>c_double_handsha<br>c_double_handsha<br>nples c_double_handsha |

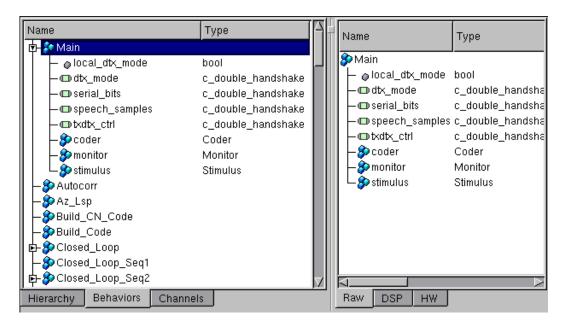

Figure 8: Design Window (Hierarchy tab).

The Design Window displays the content and the attributes of an opened design, and it allows browsing and navigation of the design hierarchy. The screenshot of the Design Window is displayed in Figure 8.

The Design Window consists of two parts: the side bar and the view pane. The side bar displays the basic information for navigation of the structure of the design. It further consists of three tabs: *Hierarchy*, *Behaviors*, and *Channels*. The view pane displays the detailed information for the entity that has been selected in the side bar.

#### 3.3.1 Hierarchy Tab

The Hierarchy tab in the side bar are illustrated in Figure 8. In the column *Name*, the design hierarchy of behaviors, channels (optional) and variables (optional) is displayed in a tree form. The hierarchy tree indicates the entity type (variable, channel or sequential, parallel, FSM, or leaf behavior) visually through icons in the *Name* column. Entities are sorted according to their calling order in the design, i.e. according to their execution order in case of sequential or FSM behavior compositions. Displaying of channels and variables in the Design Window Sidebar Hierarchy tab can be toggled via the View menu and the toolbar (see Section 4.4.4).

At the root of the hierarchy tree in the Hierarchy tab, behavior (and optionally channel) types/classes are listed. At lower levels of the hierarchy, sub-behavior (and optionally channel and/or variable) instances inside the respective parent behavior (or channel) are listed. For any but the roots of the hierarchy tree, the column *Name* shows the name and the column *Type* shows the type of the respective design instances. For classes at the root of the tree, the *Name* column shows the name of the respective class (i.e. the type) and the *Type* column is empty.

For example (Figure 8), behavior class *coder* contains three child behavior instances *pre\_process* (of type *Pre\_Process*), *coder\_12k2* (of type *Coder\_12k2*), and *post\_process* (of type *Post\_Process*), which are executed in the fsm style identified by the symbol which has two balls connected by round arrows.

If PE allocation information is available, the Hierarchy tab contains a column *PE* which shows the PE mapping information. If no PE allocation information is available, the *PE* column is not shown. If the PE mapping is empty, this implies that the behavior in this row is mapped to the same PE to which its parent is mapped.

Right-clicking on a design entity row in the Hierarchy tab opens a context menu pop-up for the selected entity. The context menu contains four commands:

**Rename** Selecting *Rename* will rename the selected entity (see Section 4.4.1).

Delete Selecting Delete will delete the selected entity (see Section 4.4.3).

- *Change Type* Selecting *Change Type* will allow plug-and-play to change the type of the selected entity. *Change Type* is not shown for the roots of the hierarchy tree.

- Set as Top Level Selecting Set as Top Level will set the selected behavior as the top level design behavior (see Section 4.5.1).

#### 3.3.2 Behaviors Tab

The Behaviors tab in the sidebar (Figure 9) lists all behavior types/classes in the design. The name of each behavior type/class is shown in a column *Name*. Behavior types are sorted by name and the sort order can be toggled by clicking into the *Name* column header.

Right-clicking on a behavior row in the Behaviors tab opens a context-menu pop-up for the selected behavior class. The context menu of the *Behaviors* tab contains three commands:

**Rename** Selecting Rename will rename the selected entity (see Section 4.4.1).

**Delete** Selecting Delete will delete the selected entity (see Section 4.4.3).

Set as Top Level Selecting Set as Top Level will set the selected behavior as the top level design behavior (see Section 4.5.1).

Figure 9: Design Window (Behaviors tab)

#### 3.3.3 Channels Tab

In the Channels tab (Figure 10), all the channel types/classes in the design are listed. The name of each channel type/class is shown in a column *Name*. Channel types are sorted by name and the sort order can be toggled by clicking into the *Name* column header.

Right-clicking on a channel row in the Channels tab opens a context-menu pop-up for the selected channel class. The context menu of the *Channels* tab contains two commands:

**Rename** Selecting *Rename* will rename the selected entity (see Section 4.4.1).

**Delete** Selecting Delete will delete the selected entity (see Section 4.4.3).

#### 3.3.4 View Pane

When clicking on a design entity row in any of the sidebar tabs, the corresponding row is selected and details of the selected entity are displayed in the view pane. The details shown are the contents of the respective entity and they include contained sub-entities including ports, methods, and variable, channel and child behavior instances. Both the name and the type of sub-entities are displayed in the *Name* and *Type* columns of the view pane, respectively. Elements of the view pane list are sorted by class (port, variable, behavior,

| Name              | Туре              |                  | Туре             |

|-------------------|-------------------|------------------|------------------|

| 🛨 💷 c_double_hand | dshake            |                  |                  |

| — 🧔 ack           | event             | 🔲 🖽 c_double_han | dshake           |

| - øreq            | event             | 📕 – 🖉 ack        | event            |

| — 🖉 tmpd          | const void *      | 📕 – 🧔 req        | event            |

| - otmpl           | unsigned long int | 📕 🗕 🖉 tmpd       | const void *     |

| - øv'             | bood              | 📕 🗕 🖉 tmpl       | unsigned long ir |

| L <sub>øw</sub>   | bool              |                  | bool             |

| <b>V</b>          |                   | L L ow           | bool             |

|                   |                   |                  |                  |

|                   |                   |                  |                  |

|                   |                   |                  |                  |

|                   |                   |                  |                  |

|                   |                   |                  |                  |

|                   |                   |                  |                  |

|                   |                   |                  |                  |

|                   |                   |                  |                  |

| Hierarchy Behavi  | ors Channels      |                  | HW I             |

| nerarchy   Benavi |                   |                  |                  |

Figure 10: Design Window (Channels tab).

channel). Within each class and among classes, the sort order can be set by clicking on the *Name* or *Type* column headers.

## 3.4 Output Window

| <b>×</b> | Compile Simulate Analyze Refine Synthesize Shell                                       |  |

|----------|----------------------------------------------------------------------------------------|--|

|          | <pre>importing Input: "VocoderSpec.ins.sir" Output: (internal representation&gt;</pre> |  |

| Rea      | v                                                                                      |  |

Figure 11: Output Window

The Output Window displays the information related to the process of SCE, such as logged status, diagnostic and error output of background commands. The screenshot of Output Window is displayed in Figure 11. The Output Window contains six tabs: *Compile*, *Simulate*, *Analyze*, *Refine*, *Synthesize*, and *Shell*. For example, the *Compile* tab displays the log messages generated during preprocessing and parsing of SpecC code when opening,

loading and importing design files. The *Refine* tab displays the log messages generated by the command line tools spawned by the main application GUI during design refinement. The Output Window is for informational purposes only and doesn't contain any button, box or context menu that users can click or edit.

The Output Window can be detached or docked. Users can drag the window (by its title bar or handle) to the desired place. If the Output Window is detached, it can be floating and displayed anywhere on the desktop. If the Output Window is docked, it has to be attached to any of the borders of the Main Window.

#### 3.5 Workspace

In general, multiple designs can be open and loaded in the SCE application. The design windows for all currently opened and loaded designs are shown in the Workspace. Within the Workspace, design windows can be minimized, maximized, resized and closed freely via their title bar, title bar icons and handles on their window frames. Closing a design window closes the corresponding design (file).

At any time, there is exactly one active design window in the Workspace. The active window is the one that has the input focus and it is visualized by highlighting its title bar. Unless otherwise noted, all menu, toolbar or other commands apply to the currently active design window. Clicking into a design window activates the corresponding window and raises it to the front of the Workspace. A newly opened design windows automatically becomes the active window.

#### 3.6 Message Boxes

As a result of certain actions, the SCE application will pop up message box dialogs for feedback to or input from the user about handling of special situations. Message boxes are used to provide informative messages and to ask simple questions. In general, there are two types of message boxes: error dialogs and information dialogs.

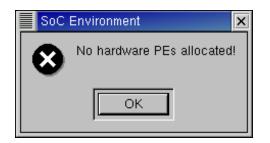

#### 3.6.1 Error Dialogs

If the application encounters an abnormal error situation in which user notification about the failure of the initiated action is required, an Error dialog will be popped up (Figure 12). The Error dialog displays an error message at the top-half of the Error dialog. At the bottom-half, an Error dialog contains one button: Ok. Clicking Ok will close the Error dialog and original dialog (if any) that prompted the message. After clicking, the original action that prompted the message is aborted and cancelled.

Figure 12: Error dialog

## 3.6.2 Information Dialogs

If the application encounters an abnormal situation in which user notification is required and the user is given several choices on how to continue, an Information dialog will be popped up (Figure 13). An information message and associated question is displayed at the top-half of the dialog. The bottom-half of the dialog contains three buttons: *Yes*, *No*, and *Cancel*. Clicking *Yes* will accept the recommendation and do the corresponding action. Clicking *No* will not accept the recommendation and will not do the corresponding action but will continue the original action that prompted the message in the first place. Finally, clicking *Cancel* will not do the recommended action and will also cancel the original action that prompted the message. Clicking one of above three buttons will close the Information dialog and original dialog (if any) that prompted the message.

| SoC Environment |                                                                                         |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------|--|--|--|

| <b>i</b>        | The file /home/work/VocoderComm.ins.sir exists already.<br>Do you want to overwrite it? |  |  |  |

|                 | <u>Y</u> es <u>N</u> o Cancel                                                           |  |  |  |

Figure 13: Information dialog

## **4** Functionality

The functionality of SCE can be classified to six categories: application, project handling, file handling, design-entity handling, synthesis, and window management.

In this section, sub-windows or sub-menus described in Section 3 are referred using the following format: *Win* : *Sub*. *Win* refers to display windows:

- Main represents the Main Window.

- Project represents the Project Window.

- Design represents the Design Window.

Sub refers to drop-down menus or sub windows (tabs):

- For the Main Window, *Sub* is either *File*, *View*, *Project*, *Synthesis*, or *Windows* (drop-down menus introduced in Section 3.1).

- For the Project Window, *Sub* is either *Models*, *Imports*, or *Sources* (tabs introduced in Section 3.2).

- For the Design Window, *Sub* is either *Hierarchy*, *Behaviors*, or *Channels* (sidebar tabs introduced in Section 3.3).

For example, *Project :: Models* refers to the Models tab in the Project Window.

Main menu or context menu commands described in Section 3 are referred to using the following format:  $Win :: Sub \Rightarrow Command$  where Command refers to a command. For example, Main::File $\Rightarrow$ Open refers to the Open command in the File menu of the Main Window menu bar. On the other hand, Project::Models $\Rightarrow$ Open refers to the Open command in the context menu of the Project Window Models tab.

### 4.1 Application

The main application of SCE supports a set of persistent application settings. Application settings are persistently stored across different invocations of the tool. In fact, application settings are shared among all tools in the SCE environment, i.e. they are persistent across invocation of different tools at different times.

Application settings are stored in both system-wide and user-specific locations. Systemwide application settings affect all users of SCE applications on the system. They are stored in a file on disk in a location that is configurable during compile time of SCE. Userspecific application settings, on the other hand, are stored in a file in the user's Linux home directory. The application first reads the system-wide and then the user-specific settings, i.e. user-specific settings can override (if given) system-wide settings and if no user-specific settings are given, application settings default to the system-wide settings. If no systemwide settings are available, compiled-in defaults are used.

Application settings in general provide the standard settings (paths, etc.) to use by default for the different parts of SCE applications. Note that application settings can be

overwritten or extended by project-specific settings (see Section 4.2). Application settings include:

- **Compiler settings** A set of options for preprocessing and parsing SpecC source files. When opening/loading or importing a design file, the SpecC compiler ('scc', see Appendix A.1) is used internally to compile the SpecC source file into SCE's internal SpecC Internal Representation (SIR) [2] format. Via the compiler settings, the options for preprocessing and parsing passed to the SpecC compiler are specified. Specifically, compiler settings contain the following:

- **Standard include path** An ordered list of directories in which to search for include files during preprocessing.

- **Standard import path** An ordered list of directories in which to search for imported files during parsing.

- Macro defines An ordered list of preprocessor macro definitions.

- Macro undefines An ordered list of preprocessor macro undefines.

- **Compiler options** Additional compiler switches passed literally to the SpecC compiler. Possible compiler switches are switches for setting warning and verbosity levels.

- **Database paths** Location of the database SIR files for the PE database, the CE database, and the bus database.

All paths in the application settings are relative to the current working directory when starting the application, i.e. relative paths in the settings are converted into absolute paths by prepending the working directory during startup of the application.

In terms of application settings, SCE supports functions to view and edit application settings/preferences.

#### 4.1.1 Preferences Editing

**Operation** Preference editing allows viewing and setting of the application settings of SCE. Users start editing the preferences of SCE by selecting *Main* ::  $Edit \Rightarrow Preference$ . This will pop-up the Edit Preferences dialog, which allow users to browse and specify the compiler and database settings. The Edit Preferences dialog is illustrated in Figure 14.

There are three tabs in the Edit Preferences dialog: Compiler, Database, and Plugins. By clicking the tab at top-left corner of the window, users can select either of them for viewing and editing.

(a) The Compiler tab allows viewing and editing of compiler settings. The screenshot for Compiler tab is shown in Figure 14. The Compiler tab contains line edit boxes

| Preferences   |                                  | x |

|---------------|----------------------------------|---|

| Compiler Da   | tabase Plugins                   |   |

|               |                                  | 1 |

|               |                                  |   |

| Include path: | \$SPECC/inc                      |   |

| Import path:  | .:\$SPECC/import                 |   |

| Library path: | \$SPECC/lib                      |   |

| Libraries:    | -Ibit -Isim -Ilonglong -Iqthread |   |

| Defines:      |                                  |   |

| Undefines:    |                                  |   |

| Options:      | -ww -v                           |   |

|               |                                  |   |

|               |                                  |   |

| Help          | OK Cancel                        |   |

Figure 14: Edit Preferences dialog (Compiler tab).

for all compiler settings. The text in the *Include Path* and *Import Path* lines defines the directory lists (separated by colons) for the standard include and standard import paths, respectively. The text in the *Defines* and *Undefines* lines define the list of macro defines and undefines (separated by semicolons), respectively. Finally, the text in the *Options* line defines the compiler options/switches.

(b) The Database tab allows for viewing and selecting of database file paths. The screenshot for Database tab is shown in Figure 15. Users can type in the file names and paths of PE, Bus and RTL databases in *PE Database*, *Bus Database*, and *RTL Database* line edit boxes. Besides typing in the databases file names, users can also select the names by using *Select* buttons next to the edit boxes. Clicking *Select* button will pop up a Database Selection dialog displayed in Figure 16

Database Selection dialog allows users to choose and select existing database files on disk to use for each of the three databases.

In the Database Selection dialog, users should first specify the database directory in *Look-in* box. The content of the directory will be automatically displayed in the display box in the center. The database type in the *File type* box defaults to SIR files for databases but can be chosen by the user. All the database files with the specified type will be displayed in the display box. Users further type in the database name in *File name* box. Finally, by clicking *Open* button, the database with the specified name will be selected. If users click *Cancel* button, then the action of database selection will be cancelled. Either clicking *Open* or *Cancel* button will close the Database Selection dialog.

Buttons *Ok* and *Cancel* appear at the bottom of the Edit Preference dialog. If users click the *Ok* button, all the edited preferences are saved. If users click the *Cancel* button, all the edited preferences are discarded. Either clicking *Ok* or *Cancel* button will close Preference dialog.

#### 4.2 **Project Handling**

Project handling deals with project issues. Project handling functionality is common and shared across all SCE tools. It allows for tracking of design meta-data over the whole lifetime of a design. A project acts as a unified container that holds all information related to a certain design at various levels of abstraction, i.e. it contains all the information that describes the organization of design files that are part of the project. Furthermore, a project contains project-specific settings that can override or extend application-specific settings (see Section 4.1) for compiler paths, options, etc. Specifically, a project contains the following information:

| Preferences                                             | ×      |

|---------------------------------------------------------|--------|

| Compiler Database Plugins                               |        |

| PE database:                                            |        |

| opt/sce-20030530/share/sce/db/processors/processors.sir | Select |

|                                                         | Edit   |

| Bus database:                                           |        |

| /opt/sce-20030530/share/sce/db/busses/busses.sir        | Select |

|                                                         | Edit   |

| RTL database:                                           |        |

| /opt/sce-20030530/share/scrtl/db/rtl.sir                | Select |

|                                                         | Edit   |

|                                                         |        |

| Help                                                    | Cancel |

Figure 15: Edit Preferences dialog (Database tab).

| Select PE          | Database                            | ×       |

|--------------------|-------------------------------------|---------|

| Look <u>i</u> n:   | 🔄 /opt/sce/share/sce/db/processors/ | 🗈 💣 🎫 🏢 |

|                    |                                     |         |

| controll           | er                                  |         |

| 📄 dsp              |                                     |         |

| 📔 🚞 general        |                                     |         |

| 📄 hw               |                                     |         |

| 📄 mem              |                                     |         |

| process            | sors.sir                            |         |

| File <u>n</u> ame: | processors.sir                      | Open    |

| File <u>t</u> ype: | SIR files (*.sir)                   | Cancel  |

Figure 16: Database Selection dialog.

- **Design models** A tree of design files and their relationship. If a design has been generated from another design through refinement, it is a child of the source design in the tree. For each model, the tree stores the design name, the location of the design's files on disk, the abstraction level, and the command used to generate the model.

- **Imports** A list of imported design files. The list of imports contains the union of all (sub-)designs imported by any of the models that are part of the project.

- **Sources** A list of source files. The list of sources contains the union of all SpecC source files from which the models that are part of the project have been compiled. For each source file, the location (path) of the file on disk is stored in the project.

- **Compiler settings** A set of project-specific options for preprocessing and parsing SpecC source files. Compiler settings contain include paths, import paths, compiler options, and macro defines and undefines. Project-specific compiler settings generally overwrite or extend the corresponding application-specific settings. In the case of paths, project paths are prepended to the standard paths defined in the application settings (i.e. they are prepended to the directory search list). In all other cases, options or macro defines/undefined are appended to the compiler command line after the standard options and macros defined in the application settings.

All paths in the project settings are defined to be relative to the location of the project file, i.e. relative paths in a project file are converted into absolute paths by appending the project file's directory during loading/opening of a project file. During saving/writing of project files, absolute paths are in turn converted back to relative paths if they point to a location below the target project file directory.

Projects are stored as text files on disk in a custom XML format. The project file format is the same for all tools in the SCE environment, i.e. a project file can be read, modified and written by any SCE tool.

Projects can be read from and saved as project files at any time in the SCE application. At any time, however, at maximum only one project can be open and loaded. While a certain project is open and loaded, its settings apply to all actions performed during that time. In addition, certain actions will automatically update and add data in the currently opened and loaded project.

In order to deal with management of projects, SCE supports a set of project handling functions. Specifically, project handling consists of the following functions:

- (a) Project Creation to create a new projects (see Section 4.2.1).

- (b) Project Opening to open and load existing projects from project files on disk (see Section 4.2.2).

- (c) Project Saving to save the current project into a project file (see Section 4.2.3).

- (d) Project Settings to edit the settings of the opened project (see Section 4.2.4).

- (e) Design Adding to adds new design files into the opened project (see Section 4.2.5).

- (f) Design Opening to open a design model or import that is part of the project (see Section 4.2.6).

- (g) Design Deletion to delete a design model file from the project and optionally the disk (see Section 4.2.7).

- (h) Design Renaming to rename a design model and design file in the project and on disk (see Section 4.2.8).

- (i) Description Changing to change the description of a design model in the opened project (see Section 4.2.9).

- (j) Project Closing to close the current project (see Section 4.2.10).

#### 4.2.1 Project Creation

**Operation** Users can create a new project by selecting *Main* :: *Project*  $\Rightarrow$  *New*.

**Error/Information Messages** Assuming before project creation, users have opened another project in SCE, the currently opened project has been modified and the opened project is not saved yet. When users select *Main* :: *Project*  $\Rightarrow$  *New*, an Information dialog will be popped up querying the user whether he wants to save the current project first before creating a new one. If the user accepts the recommendation, a Project Saving action (see Section 4.2.3) is performed first.

#### 4.2.2 Project Opening

**Operation** Users open an existing project by selecting  $Main :: Project \Rightarrow Open$ . The selection will pop-up the Project Open dialog in which the user can choose and select an existing project file on disk to open and load. The screenshot of Project Open dialog is shown in Figure 17.

Users should first specify the project directory in *Look-in* box. The content of the directory will be automatically displayed in the display box in the center. The file type defaults to project files (with a '.sce' suffix) but users can specify any file type in the *File type* box. All the project files with the specified type will be displayed in the display box. Users further select the project name in the *File name* box. Finally, by clicking *Open* button, the project with the specified name will be opened. If users click the *Cancel* button, the action of project opening will be cancelled. Either clicking *Open* or *Cancel* button will close the Project Open dialog.

|   | Open                        |                           |   |          |        | x |

|---|-----------------------------|---------------------------|---|----------|--------|---|

|   | Look <u>i</u> n:            | /home/user/work/          | Ā | <u>e</u> | k 📰 🏦  |   |

|   | 🚞<br>(=) IP<br>(=) сост. т. |                           |   |          |        |   |

|   | 🕞 SCE_Tu<br>📄 src           |                           |   |          |        |   |

|   | ocode 1                     |                           |   |          |        |   |

| F | File <u>n</u> ame:          | vocoder.sce               |   |          | Open   |   |

| F | File <u>t</u> ype:          | SCE Project Files (*.sce) |   |          | Cancel |   |

Figure 17: Project Open dialog.

**Error/Information Messages** If the specified project doesn't exist before clicking *Open* button, then clicking *Open* button has no effect.

In case of errors reading the project file from disk (file errors, wrong file format), an error dialog with a corresponding error message is popped up. Upon confirming the error, the Project Opening action is cancelled.

Assuming before project opening, users have opened another project in SCE, the opened project is modified and the opened project is not saved yet. When users open a different project, the Information dialog will be popped up to recommend users to save the previous project first and, if the recommendation is accepted, a Project Saving action will be performed. This is the same as the case in task Figure 4.2.1.

#### 4.2.3 Project Saving

**Operation** Users can save the current project by one of the following two methods:

(a) Selecting *Main* ::  $Project \Rightarrow Save$ . The project will be saved using the current project name.

If the saved project is unnamed (a new project created by task Project Creating), then selecting *Main* ::  $Project \Rightarrow Save$  will do the same action as selecting *Main* ::  $Project \Rightarrow Save As$  (see below).

(b) Users can save the current project under any (new) name by selecting Main :: Project ⇒ Save As. The selection will pop-up the Project Save dialog in which user can choose the directory and file name to save the project under. The screenshot of the Project Save dialog is displayed in Figure 18.

|   | Save As                            |                           |   | X      |

|---|------------------------------------|---------------------------|---|--------|

|   | .ook <u>i</u> n:                   | 🔄 /home/user/work/        | 7 |        |

|   | in IP<br>IP<br>In SCE_Tu<br>In src | itorial                   |   |        |

|   | ocode                              | r.sce                     |   |        |

| F | File <u>n</u> ame:                 | vocoder.sce               |   | Save   |

| F | File <u>t</u> ype:                 | SCE Project Files (*.sce) | - | Cancel |

Figure 18: Project Save dialog.

In the Project Save dialog, users should first specify the project directory in *Look-in* box. The content of the directory will be automatically displayed in the display box in the center. The file type defaults to project files ('.sce' suffix) but users can specify any file type in the *File type* box. All the project files with the specified type will be displayed in the display box. Users then select the project name in *File name* box. Finally, by clicking the *Save* button, the current project will be saved in a project file with the specified name. If users click *Cancel* button, then the action of project saving will be cancelled. Either clicking *Save* or *Cancel* button will close the Project Save dialog.

**Error/Information Messages** When selecting *Main* ::  $Project \Rightarrow Save As$  and specifying the file name of an existing file on disk, an Information dialog will pop up asking the user whether he wants to overwrite the existing file. If the user declines this, the Project Saving action will be cancelled.

When selecting *Main* :: *Project*  $\Rightarrow$  *Save* or *Main* :: *Project*  $\Rightarrow$  *Save As*, errors may occur (file errors, e.g. if no space is available on the hard disk). In this case, an Error dialog as shown in Figure 12 will be popped up, corresponding error messages will be displayed, and the Project Saving action will be cancelled.

#### 4.2.4 Project Settings Editing

**Operation** Project setting allows users to edit project settings. Unlike application preferences editing in Section 4.1.1, project setting apply only to the current project. Users start project settings editing by selecting *Main* :: *Project*  $\Rightarrow$  *Setting*. The selection will pop up

the Project Settings dialog, which is displayed in Figure 19. In the Project Settings dialog, user can view and edit the compiler and simulator settings stored in the project. For exmample, The dialog for compiler setting contains line edit boxes for all compiler settings. The text in the *Include path* and *Import path* lines defines the directory lists (separated by colons) for the project-specific include and import paths, respectively. The text in the *Defines* and *Undefines* lines define the list of macro defines and undefines (separated by semicolons), respectively. Finally, the text in the *Options* line defines the project's compiler options/switches.

| Project Settings |                                                               | X |

|------------------|---------------------------------------------------------------|---|

| Compiler Sir     | nulator                                                       |   |

|                  |                                                               |   |

|                  |                                                               |   |

| Include path:    | src/common                                                    |   |

| Import path:     | loop:src/closed_loop:src/codebook:src/update:src/processing:. |   |

| Library path:    |                                                               |   |

| Libraries:       |                                                               |   |

| Defines:         |                                                               |   |

| Undefines:       |                                                               |   |

| Options:         | -v                                                            |   |

|                  |                                                               |   |

|                  |                                                               |   |

| Help             | OK Cancel                                                     |   |

|                  |                                                               |   |

Figure 19: Project Settings dialog.

#### 4.2.5 Design Adding

**Operation** Users can add any currently opened design file to the project. In order to do that, users select *Main* ::  $Project \Rightarrow Add Design$ . After clicking, the design corresponding to the currently active design window will be added to the project. The design will be added to the project as a new root in the forest of design model trees. In addition, any imported designs and source files of the new design will be merged into the list of imports and sources that are part of the project.

**Error/Information Messages** If users try to add a file which is already in the current project, an error dialog with a corresponding error message will be popped up (as illustrated in Figure 12).

#### 4.2.6 Design Opening

**Operation** Double-clicking on a design model in the Project Window models or import tabs (*Project* :: *Models* or *Project* :: *Imports*), a File Opening action on the given design file will be performed (see Section 4.3.1 for details, including error/information messages), i.e. a corresponding design window will be opened in the workspace. If the selected design is already opened in the workspace, its design window will be raised to the top and made active. The Design Opening action can also be triggered via corresponding context menu entries in the model and import tabs (selecting *Project* :: *Models*  $\Rightarrow$  *Open* or *Project* :: *Imports*  $\Rightarrow$  *Open*).

#### 4.2.7 Design Deletion

**Operation** Users can delete files from the current project and optionally from disk. Selecting the corresponding entry in the context menu of a design model in the Project Window models tab (*Project* :: *Models*  $\Rightarrow$  *Delete*) will delete the selected design from the project and optionally from disk. In case of a model with children in the model tree, the user will also be given the option to recursively delete all the model's children.

**Error/Information Messages** After selecting *Project* :: *Models*  $\Rightarrow$  *Delete*, an Information dialog will be popped up to query to user whether he wants to also delete the corresponding model's files on disk. If the selected file has children, then another Information dialog querying the user whether he wants to also recursively delete all children and children's children of the selected model. If the selects recursive deletion, an Information dialog similar to the initial Information dialog to query about deletion of corresponding files on disk will pop up for each child model.

If file deletion on disk is selected, an error dialog may pop up in case of disk/file errors. Upon confirmation of the error, the Project Deletion action will be aborted.

#### 4.2.8 Design Renaming

**Operation** By selecting *Project* :: *Models*  $\Rightarrow$  *Rename* or by clicking into the *Design* column of the Project Window models tab, users can rename the file name displayed in the *Design* column. Renaming is performed in place inside the column cell itself by opening a corresponding text edit box. Renaming can be aborted by pressing the *Esc* key. Pressing *Enter* accepts the newly entered name and renames the design both in the project and on disk.

If the design is loaded and opened, the corresponding design window in the Workspace will also be automatically renamed.

**Error/Information Messages** If the new design name entered by the user is the name of a design already existing in the project, an Error dialog with a corresponding error message will pop up and, after confirmation, the Design Renaming action will be aborted.

If renaming the file on disk results in an error (file error), a corresponding Error dialog will be popped up and the Design Renaming will be aborted.

# 4.2.9 Description Changing

**Operation** Users can change the file description displayed in the *Description* column of *Project* :: *Models* tab by selecting the *Project* :: *Models*  $\Rightarrow$  *Change Description* context menu entry or by clicking into the corresponding *Description* column in the row representing the selected file. After clicking, the corresponding cell in the *Description* column of *Project* :: *Models* is editable in place. Editing can be aborted with *Esc* and is accepted by pressing *Enter*.

#### 4.2.10 Project Closing

**Operation** Users can close the current project by selecting  $Main :: Project \Rightarrow Close$ .

**Error/Information Messages** If the current project is modified and not yet saved, selecting *Close* will pop up an Information dialog which recommends to save the current project first. If the user accepts the recommendation, a Project Saving action (Section 4.2.3) is performed before closing the project.